|     | REVISIONS                                                    |          |                   |  |  |  |  |

|-----|--------------------------------------------------------------|----------|-------------------|--|--|--|--|

| LTR | DESCRIPTION                                                  | DATE     | APPROVED          |  |  |  |  |

| A   | Update boilerplate paragraphs to current requirements. – RDC | 25-03-19 | Muhammad A. Akbar |  |  |  |  |

|     |                                                              |          |                   |  |  |  |  |

Vendor item drawing

Prepared in accordance with ASME Y14.24

REV А А А А А А А А А PAGE 128 129 130 131 132 133 134 135 136 REV А А А А А А А А А А А А А А А А А А А А А А PAGE 106 107 108 109 110 111 112 113 114 115 117 118 119 120 121 122 123 124 125 126 127 116 REV А А А А А А А А А А А А А А А А А А А А А А PAGE 84 97 85 86 87 88 89 90 91 92 93 94 95 96 98 99 100 101 102 103 104 105 REV А А А А А А А А А А A А А А А А А А А А А A PAGE 62 75 63 64 65 66 67 68 69 70 71 72 73 74 76 77 78 79 80 81 82 83 REV А А А А А А А А А А А А А А А А А А А А А А PAGE 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 61 60 REV А А А А А А А А А А А А А А А А А А А А А A PAGE 18 20 21 19 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 REV A A А А А А A А А А А А А А А A А **REV STATUS OF PAGES** PAGE 2 3 4 5 6 7 8 10 11 12 13 15 16 17 9 14 1 PREPARED BY **DLA LAND AND MARITIME** PMIC N/A COLUMBUS, OHIO 43218-3990 Phu H. Nguyen https://www.dla.mil/landandmaritime CHECKED BY Original date of drawing TITLE YY MM DD MICROCIRCUIT, LINEAR-DIGITAL, Phu H. Nguyen PROCESSOR, MONOLITHIC SILICON 19-05-17 APPROVED BY Thomas M. Hess SIZE CODE IDENT. NO. DWG NO. V62/15602 Α 16236 Α PAGE 1 **OF** 136 REV

#### 1. SCOPE

1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance Processor microcircuit, with an operating temperature range of -40°C to +105°C.

1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

| V62/15602<br>Drawing<br>number | - <u>01</u><br>Device type<br>(See 1.2.1) | Case outline<br>(See 1.2.2) | Lead finish<br>(See 1.2.3) |

|--------------------------------|-------------------------------------------|-----------------------------|----------------------------|

| 1.2.1 Device type(s).          |                                           |                             |                            |

| Device type                    | Generic                                   | <u>Ci</u>                   | rcuit function             |

| 01                             | AM3558 –EP                                |                             | Processor                  |

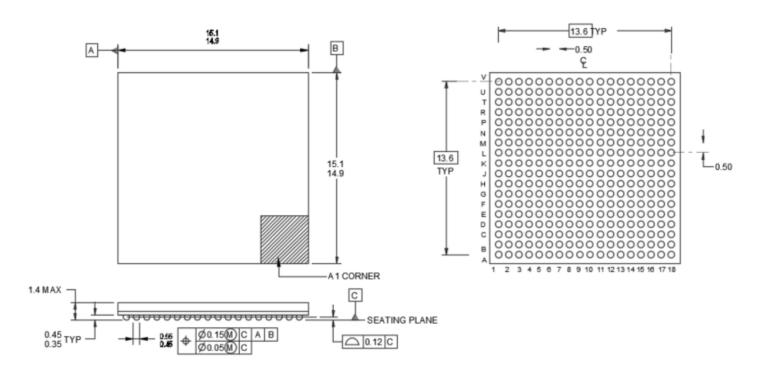

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

| Outline letter | <u>Number of pins</u> | Package style                      |

|----------------|-----------------------|------------------------------------|

| Х              | 324                   | Plastic Ball Grid Array <u>1</u> / |

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator          | <u>Material</u>                                                                                                          |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------|

| A<br>B<br>C<br>D<br>E<br>F | Hot solder dip<br>Tin-lead plate<br>Gold plate<br>Palladium<br>Gold flash palladium<br>Tin-lead alloy (BGA/CGA)<br>Other |

| £                          | Culoi                                                                                                                    |

<u>1</u>/ Devices listed on this drawing are supplied to lead finish "F". The solder ball material contains compositions of Sn = 63%, Pb = 34.5, Ag = 2% and Sb = 0.5%.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV A          | PAGE 2                   |

#### 1.3 Absolute maximum ratings. 1/2/

Over junction temperature range (unless otherwise noted)

|                                                                 | -                                                             | Min  | Max                           | Unit         |

|-----------------------------------------------------------------|---------------------------------------------------------------|------|-------------------------------|--------------|

| VDD_MPU                                                         | Supply voltage for the MPU core domain                        | -0.5 | 1.5                           | V            |

| VDD_CORE                                                        | Supply voltage for the core domain                            | -0.5 | 1.5                           | V            |

| CAP_VDD_RTC <u>3</u> /                                          | Supply voltage for the RTC core domain                        | -0.5 | 1.5                           | V            |

| VPP <u>4</u> /                                                  | Supply voltage for the RTC domain                             | -0.5 | 2.2                           | V            |

| VDDS_RTC                                                        | Supply voltage for the RTC domain                             | -0.5 | 2.1                           | V            |

| VDDS_OSC                                                        | Supply voltage for the System oscillator                      | -0.5 | 2.1                           | V            |

| VDDS_SRAM_CORE_BG                                               | Supply voltage for the Core SRAM LDOs                         | -0.5 | 2.1                           | V            |

| VDDS_SRAM_MPU_BB                                                | Supply voltage for the MPU SRAM LDOs                          | -0.5 | 2.1                           | V            |

| VDDS_PLL_DDR                                                    | Supply voltage for the DPLL DDR                               | -0.5 | 2.1                           | V            |

| VDDS_PLL_CORE_LCD                                               | Supply voltage for the DPLL Core and LCD                      | -0.5 | 2.1                           | V            |

| VDDS_PLL_MPU                                                    | Supply voltage for the DPLL MPU                               | -0.5 | 2.1                           | V            |

| VDDS_DDR                                                        | Supply voltage for the DDR IO domain                          | -0.5 | 2.1                           | V            |

| VDDS                                                            | Supply voltage for all dual-voltage IO domains                | -0.5 | 2.1                           | V            |

| VDDA1P8V_USB0                                                   | Supply voltage for USBPHY                                     | -0.5 | 2.1                           | V            |

| VDDA1P8V_USB1                                                   | Supply voltage for USBPHY                                     | -0.5 | 2.1                           | V            |

| VDDA_ADC                                                        | Supply voltage for ADC                                        | -0.5 | 2.1                           | V            |

| VDDSHV1                                                         | Supply voltage for the dual-voltage IO domain                 | -0.5 | 3.8                           | V            |

| VDDSHV2                                                         | Supply voltage for the dual-voltage IO domain                 | -0.5 | 3.8                           | V            |

| VDDSHV3                                                         | Supply voltage for the dual-voltage IO domain                 | -0.5 | 3.8                           | V            |

| VDDSHV4                                                         | Supply voltage for the dual-voltage IO domain                 | -0.5 | 3.8                           | V            |

| VDDSHV5                                                         | Supply voltage for the dual-voltage IO domain                 | -0.5 | 3.8                           | V            |

| VDDSHV6                                                         | Supply voltage for the dual-voltage IO domain                 | -0.5 | 3.8                           | V            |

| VDDA3P3V_USB0                                                   | Supply voltage for USBPHY                                     | -0.5 | 4                             | V            |

| VDDA3P3V_USB1                                                   | Supply voltage for USBPHY                                     | -0.5 | 4                             | V            |

| USB0_VBUS 5/                                                    | Supply voltage for USB VBUS comparator input                  | -0.5 | 5.25                          | V            |

| USB1_VBUS <u>5</u> /                                            | Supply voltage for USB VBUS comparator input                  | -0.5 | 5.25                          | V            |

| DDR_VREF                                                        | Supply voltage for the DDR SSTL and HSTL<br>reference voltage | -0.5 | 1.1                           | V            |

| Steady state max voltage at all IO pins <u>6</u> /              |                                                               |      | IO supply vo                  | ltage +0.3 V |

| USB0_ID <u>7</u> /                                              | Steady state maximum voltage for the USB ID input             | -0.5 | 2.1                           | V            |

| USB1_ID <u>7</u> /                                              | Steady state maximum voltage for the USB ID input             | -0.5 | 2.1                           | V            |

| Transient overshoot and undershoot specification at IO terminal |                                                               |      | responding IC<br>up to 30% of |              |

| Latch-up performance <u>8</u> /                                 | Class II (105°C)                                              | 45   |                               | mA           |

| Junction temperature, TJ                                        |                                                               | -40  | 125                           | °C           |

| Storage temperature, Tstg <u>9</u> /                            |                                                               | -55  | 155                           | °C           |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV A          | PAGE 3                   |

#### 1.4 ESD ratings.

| Electrostatic discharge (ESD) performance (VESD):         |     |

|-----------------------------------------------------------|-----|

| Human Body Model (HBM), per ANSI/ESDA/JEDEC JS001 ±2000 V | 10/ |

| Charged Device Model (CDM), per JESD22-C101 ±500 V        | 11/ |

#### 1.5 Power-On Hours (POH).

Reliability Data 12/ 13/ 14/ 15/

| Operating Condition | EX                              | TENDED                     |

|---------------------|---------------------------------|----------------------------|

| Operating Condition | Junction Temp (T <sub>J</sub> ) | Lifetime (POH) <u>16</u> / |

| Turbo               | –40°C to 105°C                  | 80K                        |

| OPP120              | –40°C to 105°C                  | 100K                       |

| OPP100              | –40°C to 105°C                  | 100K                       |

| OPP50               | –40°C to 105°C                  | 100K                       |

- 2/ All voltage values are with respect to their associated VSS or VSSA x.

- 3/ This supply is sourced from an internal LDO when RTC\_KALDO\_ENn is low. If RTC\_KALDO\_ENn is high, this supply must be sourced from an external power supply.

- 4/ During functional operation, this pin is a no connect.

- 5/ This terminal is connected to a fail-safe IO and does not have a dependence on any IO supply voltage.

- 6/ This parameter applies to all IO terminals which are not fail-safe and the requirement applies to all values of IO supply voltage. For example, if the voltage applied to a specific IO supply is 0 volts the valid input voltage range for any IO powered by that supply will be -0.5 to +0.3 V. Apply special attention anytime peripheral devices are not powered from the same power sources used to power the respective IO supply. It is important the attached peripheral never sources a voltage outside the valid input voltage range, including power supply ramp-up and ramp-down sequences.

- 7/ This terminal is connected to analog circuits in the respective USB PHY. The circuit sources a known current while measuring the voltage to determine if the terminal is connected to VSSA\_USB with a resistance less than 10 Ω or greater than 100 kΩ. The terminal should be connected to ground for USB host operation or open-circuit for USB peripheral operation, and should never be connected to any external voltage source.

- 8/ Based on JEDEC JESD78D [IC Latch-Up Test].

- 9/ For tape and reel the storage temperature range is [-10°C; +50°C] with a maximum relative humidity of 70%. TI recommends returning to ambient room temperature before usage.

- 10/ JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- 11/ JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

- 12/ The power-on hours (POH) information in this table is provided solely for your convenience and does not extend or modify the warranty provided under TI's standard terms and conditions for TI semiconductor products.

- 13/ To avoid significant degradation, the device power-on hours (POH) must be limited as described in this table.

- 14/ Logic functions and parameter values are not assured out of the range specified in the recommended operating conditions.

- 15/ The above notations cannot be deemed a warranty or deemed to extend or modify the warranty under TI's standard terms and conditions for TI semiconductor products

- 16/ POH = Power-on hours when the device is fully functional.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV A          | PAGE 4                   |

<sup>1/</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 1.6 Operating Performance Points (OPPs).

VDD\_CORE OPPs for Case X Package 17/

| VDD_CORE OPP        |         | VDD_CORE |         | DDR3 <u>18</u> | DDR2 18/         | mDDR 18/           | L3 and L4       |

|---------------------|---------|----------|---------|----------------|------------------|--------------------|-----------------|

| Device Rev. "Blank" | Min     | NOM      | Max     | DDR3L          | DDR2 <u>10</u> / | 11100R <u>10</u> / | LS and L4       |

| OPP100              | 1.056 V | 1.100 V  | 1.144 V | 400 MHz        | 266 MHz          | 200 MHz            | 200 and 100 MHz |

| OPP50               | 0.912 V | 0.950 V  | 0.998 V |                | 125 MHz          | 90 MHz             | 100 and 50 MHz  |

Valid Combinations of VDD\_CORE and VDD\_MPU OPPs for case X Package 17/ 18/

| VDD_CORE | VDD_MPU |

|----------|---------|

| OPP50    | OPP100  |

| OPP100   | OPP100  |

| OPP100   | OPP120  |

| OPP100   | Turbo   |

#### VDD\_MPU OPPs for Case X Package 17/

|             | VDD_MPU |         |         |          |

|-------------|---------|---------|---------|----------|

| VDD_MPU OPP | Min     | NOM     | Max     | ARM (A8) |

| Turbo       | 1.210 V | 1.260 V | 1.326 V | 800 MHz  |

| OPP120      | 1,152 V | 1.200 V | 1.248 V | 720 MHz  |

| OPP100      | 1.056 V | 1.100 V | 1.144 V | 600 MHz  |

| OPP100      | 0.912 V | 0.950 V | 0.988 V | 300 MHz  |

Valid Combinations of VDD\_CORE and VDD\_MPU OPPs for case X Package

| VDD_CORE | VDD_MPU |

|----------|---------|

| OPP50    | OPP50   |

| OPP50    | OPP100  |

| OPP100   | OPP50   |

| OPP100   | OPP100  |

| OPP100   | OPP120  |

| OPP100   | Turbo   |

|          |         |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV A          | PAGE 5                   |

<sup>&</sup>lt;u>17</u>/ Frequencies in this table indicate maximum performance for a given OPP condition.

<sup>18/</sup> This parameter represents the maximum memory clock frequency. Since data is transferred on both edges of the clock, double data rate (DDR), the maximum data rate is two times the maximum memory clock frequency defined in this table.

### 1.7 <u>Recommended operating conditions</u>.

Over junction temperature range (unless otherwise noted)

| SUPPLY NAME              | DESCRIPTION                                                | Min   | NOM   | Max   | Unit |

|--------------------------|------------------------------------------------------------|-------|-------|-------|------|

| VDD_CORE <u>19</u> /     | Supply voltage range for core domain; OPP100               | 1.056 | 1.100 | 1.144 | V    |

|                          | Supply voltage range for core domain; OPP50                | 0.912 | 0.950 | 0.988 |      |

|                          | Supply voltage range for MPU domain; Turbo                 | 1.210 | 1.260 | 1.326 |      |

|                          | Supply voltage range for MPU domain; OPP120                | 1.152 | 1.200 | 1.248 |      |

| VDD_MPU <u>19</u> /      | Supply voltage range for MPU domain; OPP100                | 1.056 | 1.100 | 1.144 | V    |

|                          | Supply voltage range for MPU domain; OPP50                 | 0.912 | 0.950 | 0.988 |      |

| CAP_VDD_RTC 20/          | Supply voltage range for RTC domain input                  | 0.900 | 1.100 | 1.250 | V    |

| VDDS_RTC                 | Supply voltage range for RTC domain                        | 1.710 | 1.800 | 1.890 | V    |

|                          | Supply voltage range for DDR IO domain (DDR2)              | 1.710 | 1.800 | 1.890 |      |

| VDDS_DDR                 | Supply voltage range for DDR IO domain (DDR3)              | 1.425 | 1.500 | 1.575 | V    |

|                          | Supply voltage range for DDR IO domain (DDR3L)             | 1.283 | 1.350 | 1.418 | 1    |

| VDDS <u>21</u> /         | Supply voltage range for all dual-voltage IO domains       | 1.710 | 1.800 | 1.890 | V    |

| VDDS_SRAM_CORE_BG        | Supply voltage range for Core SRAM LDOs, analog            | 1.710 | 1.800 | 1.890 | V    |

| VDDS_SRAM_MPU_BB         | Supply voltage range for MPU SRAM LDOs, analog             | 1.710 | 1.800 | 1.890 | V    |

| VDDS_PLL_DDR 22/         | Supply voltage range for DPLL DDR, analog                  | 1.710 | 1.800 | 1.890 | V    |

| VDDS_PLL_CORE_LCD<br>22/ | Supply voltage range for DPLL CORE and LCD, analog         | 1.710 | 1.800 | 1.890 | V    |

| VDDS_PLL_MPU 22/         | Supply voltage range for DPLL MPU, analog                  | 1.710 | 1.800 | 1.890 | V    |

| VDDS_OSC                 | Supply voltage range for system oscillator IO's, analog    | 1.710 | 1.800 | 1.890 | V    |

| VDDA1P8V_USB0 22/        | Supply voltage range for USBPHY and PER DPLL analog, 1.8 V | 1.710 | 1.800 | 1.890 | V    |

| VDDA1P8V_USB1            | Supply voltage range for USB PHY, analog, 1.8 V            | 1.710 | 1.800 | 1.890 | V    |

| VDDA3P3V_USB0            | Supply voltage range for USB PHY, analog, 3.3 V            | 3.135 | 3.300 | 3.465 | V    |

| VDDA3P3V_USB1            | Supply voltage range for USB PHY, analog, 3.3 V            | 3.135 | 3.300 | 3.465 | V    |

| VDDA_ADC                 | Supply voltage range for ADC, analog                       | 1.710 | 1.800 | 1.890 | V    |

| VDDSHV1                  |                                                            | 1.710 | 1.800 | 1.890 | V    |

| VDDSHV2                  | _                                                          | 1.710 | 1.800 | 1.890 | V    |

| VDDSHV3                  | Supply voltage range for dual-voltage IO domain            |       | 1.800 | 1.890 | V    |

| VDDSHV4                  | (1.8-V operation)                                          | 1.710 | 1.800 | 1.890 | V    |

| VDDSHV5                  |                                                            | 1.710 | 1.800 | 1.890 | V    |

| VDDSHV6                  |                                                            | 1.710 | 1.800 | 1.890 | V    |

| VDDSHV1                  | Supply voltage range for dual-voltage IO domain            | 3.135 | 3.300 | 3.465 | V    |

| VDDSHV2                  | (3.3-V operation)                                          | 3.135 | 3.300 | 3.465 | V    |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |

|                       |      | REV A          | PAGE 6                   |

#### 1.7 <u>Recommended operating conditions</u>- Continued.

Over junction temperature range (unless otherwise noted)

| SUPPLY NAME                                 | DESCRIPTION                                 | Min      | NOM         | Max      | Unit |

|---------------------------------------------|---------------------------------------------|----------|-------------|----------|------|

| VDDSHV3                                     |                                             | 3.135    | 3.300       | 3.465    | V    |

| VDDSHV4                                     | Supply voltage range for dual-voltage IO    | 3.135    | 3.300       | 3.465    | V    |

| VDDSHV5                                     | domain (3.3 -V operation)                   | 3.135    | 3.300       | 3.465    | V    |

| VDDSHV6                                     |                                             | 3.135    | 3.300       | 3.465    | V    |

| DDR_VREF                                    | Voltage range for DDR SSTL and HSTL         | 0.49 ×   | 0.49 ×      | 0.49 ×   | V    |

|                                             | reference input (DDR2, DDR3, DDR3L)         | VDDS_DDR | VDDS_DDR    | VDDS_DDR |      |

| USB0_VBUS                                   | Voltage range for USB VBUS comparator input | 0.000    | 5.000       | 5.250    | V    |

| USB1_VBUS                                   |                                             | 0.000    | 5.000       | 5.250    | V    |

| USB0_ID                                     | Voltage range for the USB ID input          |          | <u>23</u> / |          | V    |

| USB1_ID                                     |                                             |          | <u>23</u> / |          | V    |

| Operating temperature range, T <sub>J</sub> | Extended temperature                        | -40      |             | 105      | °C   |

#### 1.8 Thermal characteristics.

| Thermal metric <u>3</u> /            | Case outline X<br>(°C/W) <u>24</u> / <u>25</u> / | AIR FLOW<br>(m/s) <u>26</u> / |

|--------------------------------------|--------------------------------------------------|-------------------------------|

| Junction to case, Reuc               | 10.2                                             | N/A                           |

| Junction to board, Rejb              | 12.1                                             | N/A                           |

|                                      | 24.2                                             | 0                             |

| Junction to free air, ROJA           | 20.1                                             | 1.0                           |

|                                      | 19.3                                             | 2.0                           |

|                                      | 18.8                                             | 3.0                           |

|                                      | 0.3                                              | 0.0                           |

| Junction-to-package top, $\phi_{JT}$ | 0.6                                              | 1.0                           |

|                                      | 0.7                                              | 2.0                           |

|                                      | 0.8                                              | 3.0                           |

|                                      | 12.7                                             | 0.0                           |

| Junction-to-board, $\phi_{JB}$       | 12.3                                             | 1.0                           |

|                                      | 12.3                                             | 2.0                           |

|                                      | 12.2                                             | 3.0                           |

- 19/ The supply voltage defined by OPP100 should be applied to this power domain before the device is released from reset.

- 20/ This supply is sourced from an internal LDO when RTC\_KALDO\_ENn is low. If RTC\_KALDO\_ENn is high, this supply must be sourced from an external power supply.

- 21/ VDDS should be supplied irrespective of 1.8- or 3.3-V mode of operation of the dual-voltage IOs.

- 22/ For more details on power supply requirements, see Section 6.1.4 from manufacturer data.

- $\overline{23}$ / This terminal is connected to analog circuits in the respective USB PHY. The circuit sources a known current while measuring the voltage to determine if the terminal is connected to VSSA\_USB with a resistance less than 10  $\Omega$  or greater than 100 k $\Omega$ . The terminal should be connected to ground for USB host operation or open-circuit for USB peripheral operation, and should never be connected to any external voltage source.

- 24/ These values are based on a JEDEC-defined 2S2P system (with the exception of the theta JC [ROJC] value, which is based on a JEDEC-defined 1S0P system) and will change based on environment as well as application. For more information, see these EIA/JEDEC standards:JESD51-2, JESD51-3, JESD51-7, JESD51-9,

- <u>25</u>/ °C/W = degrees Celsius per watt.

- <u>26</u>/ m/s = meters per second.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV A          | PAGE 7                   |

#### 1.9 **Power Consumption Summary.**

#### Maximum Current Ratings at Power Terminals 27/

| SUPPLY NAME             | DESCRIPTION                                            | Max                                                  | Unit |    |

|-------------------------|--------------------------------------------------------|------------------------------------------------------|------|----|

|                         | Maximum current rating for the core domain; OPP100     |                                                      | 400  |    |

| VDD_CORE                | Maximum current rating for the core domain; OPP50      | Maximum current rating for the core domain; OPP50    |      |    |

|                         | Maximum current rating for the MPU domain; Turbo       | at 800 MHz                                           | 800  |    |

|                         | Maximum current rating for the MPU domain; OPP120      | at 720 MHz                                           | 720  |    |

| VDD_MPU                 | Maximum current rating for the MPU domain; OPP100      | at 600 MHz                                           | 600  |    |

|                         | Maximum current rating for the MPU domain; OPP50       | at 400 MHz                                           | 300  |    |

| CAP_VDD_RTC <u>28</u> / | Maximum current rating for RTC domain input and LDO of | output                                               | 2    |    |

| VDDS_RTC                | Maximum current rating for the RTC domain              |                                                      | 5    |    |

| VDDS_DDR                | Maximum current rating for DDR IO domain               |                                                      | 250  |    |

| VDDS                    | Maximum current rating for all dual-voltage IO domains |                                                      | 50   |    |

| VDDS_SRAM_CORE_BG       | Maximum current rating for core SRAM LDOs              | 10                                                   |      |    |

| VDDS_SRAM_MPU_BB        | Maximum current rating for MPU SRAM LDOs               |                                                      | 10   | mA |

| VDDS_PLL_DDR            | Maximum current rating for the DPLL DDR                | 10                                                   |      |    |

| VDDS_PLL_CORE_LCD       | Maximum current rating for the DPLL Core and LCD       |                                                      | 20   |    |

| VDDS_PLL_MPU            | Maximum current rating for the DPLL MPU                |                                                      | 10   |    |

| VDDS_OSC                | Maximum current rating for the system oscillator IOs   | laximum current rating for the system oscillator IOs |      |    |

| VDDA1P8V_USB0           | Maximum current rating for USBPHY 1.8 V                | aximum current rating for USBPHY 1.8 V               |      |    |

| VDDA1P8V_USB1           | Maximum current rating for USBPHY 1.8 V                |                                                      | 25   |    |

| VDDA3P3V_USB0           | Maximum current rating for USBPHY 3.3 V                |                                                      | 40   |    |

| VDDA3P3V_USB1           | Maximum current rating for USBPHY 3.3 V                |                                                      | 40   |    |

| VDDA_ADC                | Maximum current rating for ADC                         |                                                      | 10   |    |

| VDDSHV1                 | Maximum current rating for dual-voltage IO domain      |                                                      | 50   |    |

| VDDSHV2                 | Maximum current rating for dual-voltage IO domain      |                                                      | 50   |    |

| VDDSHV3                 | Maximum current rating for dual-voltage IO domain      |                                                      | 50   | 7  |

| VDDSHV4                 | Maximum current rating for dual-voltage IO domain      |                                                      | 50   | 7  |

| VDDSHV5                 | Maximum current rating for dual-voltage IO domain      |                                                      | 50   |    |

| VDDSHV6                 | Maximum current rating for dual-voltage IO domain      |                                                      | 100  |    |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV A          | PAGE 8                   |

<sup>27/</sup> Current ratings specified in this table are worst-case estimates. Actual application power supply estimates could be lower. For more information, see the manufacturer AM335x Power Consumption Summary application report (SPRABN5) on manufacturer data.

<sup>28/</sup> This supply is sourced from an internal LDO when RTC\_KALDO\_ENn is low. If RTC\_KALDO\_ENn is high, this supply must be sourced from an external power supply.

# 1.9 **Power Consumption Summary**- Continued.

# Low-Power Modes Power Consumption Summary

| POWER<br>MODES | APPLICATION STATE                                                                                                                                                                                                                                                                                                                                                               | POWER DOMAINS, CLOCKS, AND<br>VOLTAGE SUPPLY STATES                                                                                                                                                                                                                                                                                                                              | NOM  | Max  | Unit |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| Standby        | DDR memory is in self-refresh<br>and contents are preserved.<br>Wake up from any GPIO. Cortex-<br>A8 context/register contents are<br>lost and must be saved before<br>entering standby. On exit,<br>context must be restored from<br>DDR. For wake-up, boot ROM<br>executes and branches to<br>system resume.                                                                  | <ul> <li>Power supplies:</li> <li>All power supplies are ON.</li> <li>VDD_MPU = 0.95 V (nom)</li> <li>VDD_CORE = 0.95 V (nom)</li> <li>Clocks:</li> <li>Main Oscillator (OSC0) = ON</li> <li>All DPLLs are in bypass.</li> <li>Power domains:</li> <li>PD_PER = ON</li> <li>PD_MPU = OFF</li> <li>PD_GFX = OFF</li> <li>PD_WKUP = ON</li> <li>DDR is in self-refresh.</li> </ul> | 16.5 | 22.0 | mW   |

| Deepsleep1     | On-chip peripheral registers are<br>preserved. Cortex-A8<br>context/registers are lost, so the<br>application needs to save them<br>to the L3 OCMC RAM or DDR<br>before entering DeepSleep. DDR<br>is in self- refresh. For wake-up,<br>boot ROM executes and<br>branches to syste                                                                                              | Power supplies:<br>• All power supplies are ON.<br>• VDD_MPU = 0.95 V (nom)<br>• VDD_CORE = 0.95 V (nom)<br>Clocks:<br>• Main Oscillator (OSC0) = OFF<br>• All DPLLs are in bypass.<br>Power domains:<br>• PD_PER = ON<br>• PD_MPU = OFF<br>• PD_GFX = OFF<br>• PD_GFX = OFF<br>• PD_WKUP = ON<br>DDR is in self-refresh.                                                        | 6.0  | 10.0 |      |

| Deepsleep0     | PD_PER peripheral and Cortex-<br>A8/MPU register information will<br>be lost. On- chip peripheral<br>register (context) information of<br>PD-PER domain needs to be<br>saved by application to SDRAM<br>before entering this mode. DDR<br>is in self- refresh. For wake-up,<br>boot ROM executes and<br>branches to peripheral context<br>restore followed by system<br>resume. | Power supplies:<br>• All power supplies are ON.<br>• VDD_MPU = 0.95 V (nom)<br>• VDD_CORE = 0.95 V (nom)<br>Clocks:<br>• Main Oscillator (OSC0) = OFF<br>• All DPLLs are in bypass.<br>Power domains:<br>• PD_PER = OFF<br>• PD_MPU = OFF<br>• PD_GFX = OFF<br>• PD_GFX = OFF<br>• PD_WKUP = ON<br>DDR is in self-refresh.                                                       | 3.0  | 4.3  |      |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |  |

|-----------------------|------|----------------|--------------------------|--|

| COLUMBUS, OHIO        | A    | 16236          |                          |  |

|                       |      | REV A          | PAGE 9                   |  |

#### 2. APPLICABLE DOCUMENTS

#### JEDEC - SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

| JEP95<br>JEP155<br>JEP157 |   | Registered and Standard Outlines for Semiconductor Devices<br>Recommended ESD Target Levels For HBM/MM Qualification<br>Recommended ESD-CDM Target Levels |

|---------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| JESD 51-2                 | _ | · · · · · · · · · · · · · · · · · · ·                                                                                                                     |

| JESD 51-3                 | _ | Low Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages.                                                                          |

| JESD51-7                  | _ | High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages                                                                          |

| JESD51-9                  | _ | Test Boards for Area Array Surface Mount Package Thermal Measurements.                                                                                    |

| JESD79-2F                 | _ | DDR2 SDRAM specification.                                                                                                                                 |

| JESD79-3F                 | _ | DDR2 SDRAM specification.                                                                                                                                 |

| JESD209B                  | _ | Low Power Double Data Rate (LPDDR).                                                                                                                       |

(Copies of these documents are available online at https://www.jedec.org.)

#### 3. REQUIREMENTS

3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

3.4 Design, construction, and physical dimension. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

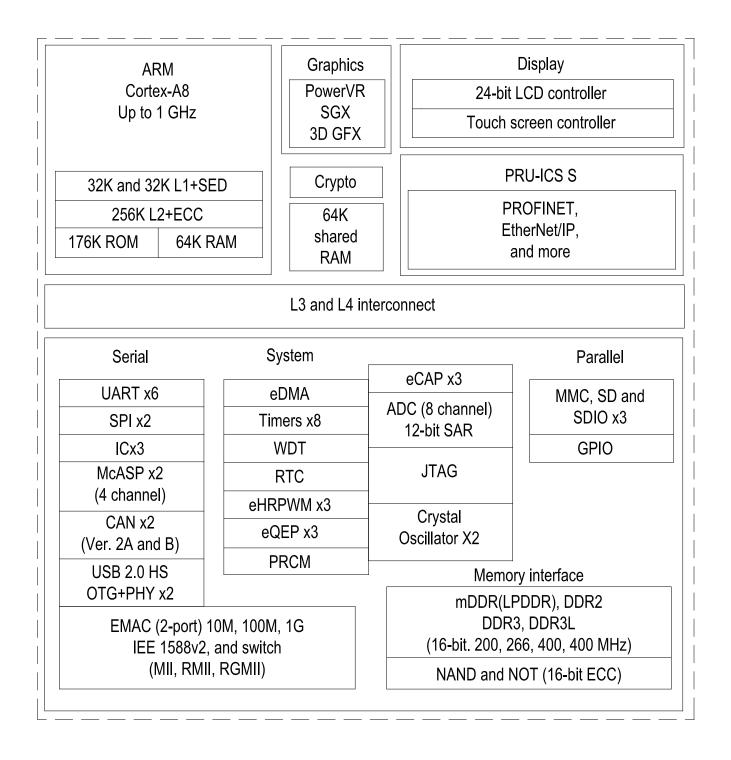

- 3.5.2 <u>Functional block diagram</u>. The functional block diagram shall be as shown in figure 2.

- 3.5.3 Pin Map Location (Section Left). Pin Map Location (Section Left) shall be as shown in figure 3.

- 3.5.4 Pin Map Location (Section Middle). Pin Map Location (Section Middle) shall be as shown in figure 4.

- 3.5.5 Pin Map Location (Section Right). Pin Map Location (Section Right) shall be as shown in figure 5.

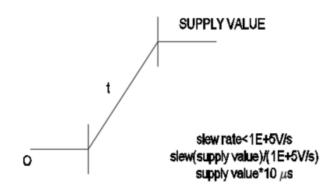

- 3.5.6 Power Supply and Slew Rate. The Power Supply and Slew Rate shall be as shown in figure 6.

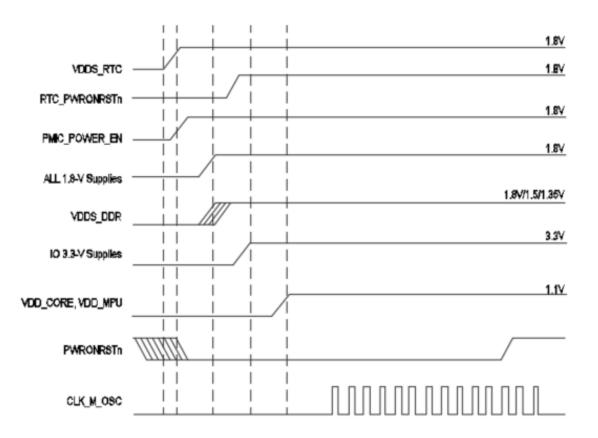

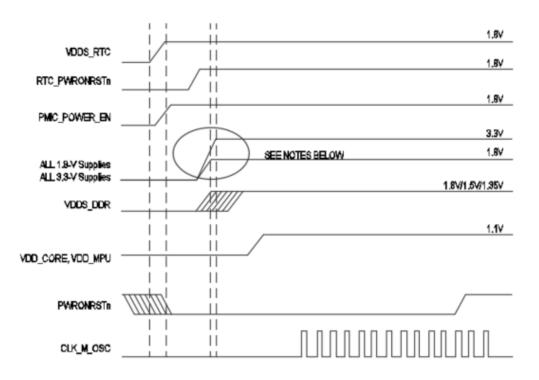

- 3.5.7 <u>Preferred Power Supply Sequencing with Dual Voltage IOs Configured as 3.3 V</u>. The Preferred Power Supply Sequencing with Dual Voltage IOs Configured as 3.3 V shall be as shown in figure 7.

- 3.5.8 <u>Alternate Power Supply Sequencing with Dual Voltage IOs Configured as 3.3 V</u>. The Alternate Power Supply Sequencing with Dual Voltage IOs Configured as 3.3 V shall be as shown in figure 8.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |

|                       |      | REV A          | PAGE 10                  |

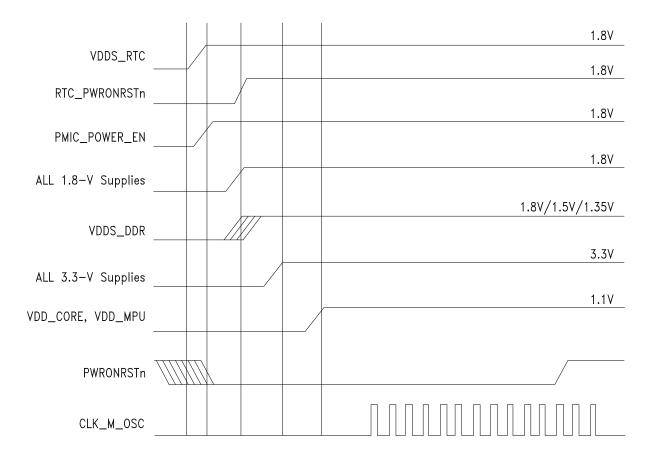

- 3.5.9 <u>Power Supply Sequencing with Dual Voltage IOs Configured as 1.8 V</u>. The Power Supply Sequencing with Dual Voltage IOs Configured as 1,8 V shall be as shown in figure 9.

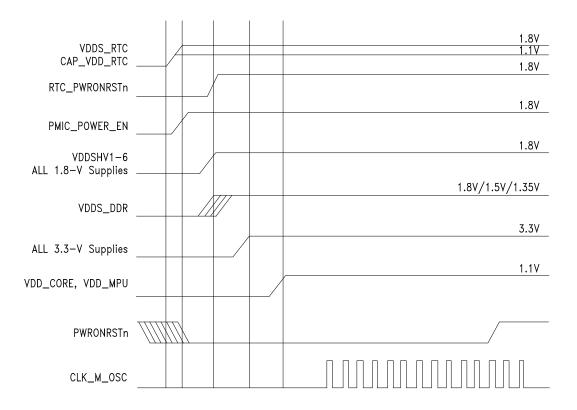

- 3.5.10 <u>Power-Supply Sequencing With Internal RTC LDO Disabled</u>. The Power-Supply Sequencing With Internal RTC LDO Disabled shall be as shown in figure 10.

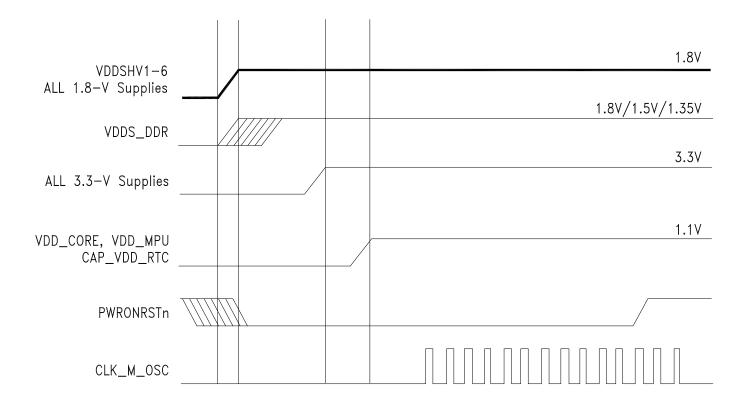

- 3.5.11 <u>Power-Supply Sequencing with RTC Feature Disabled</u>. The Power-Supply Sequencing with RTC Feature Disabled shall be as shown in figure 11.

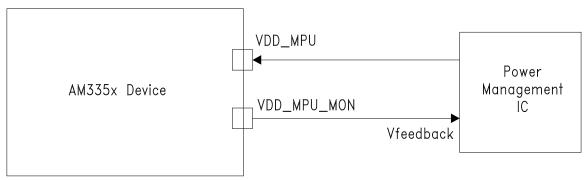

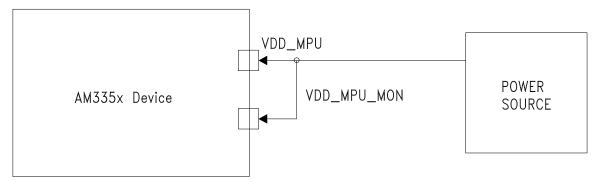

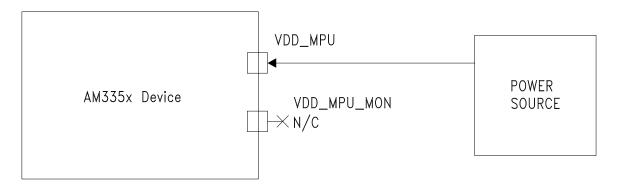

- 3.5.12 <u>VDD\_MPU\_MON\_Connectivity</u>. The VDD\_MPU\_MON Connectivity shall be as shown in figure 12.

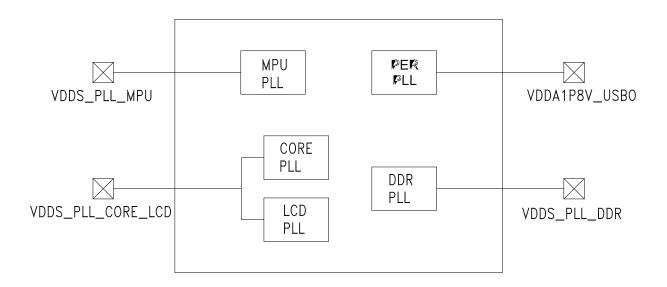

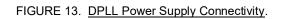

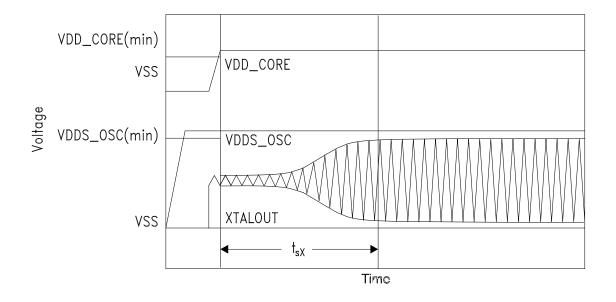

- 3.5.13 <u>DPLL Power Supply Connectivity</u>. The DPLL Power Supply Connectivity shall be as shown in figure 13.

- 3.5.14 OSC0 Start-Up Time. The OSC0 Start-Up Time shall be as shown in figure 14.

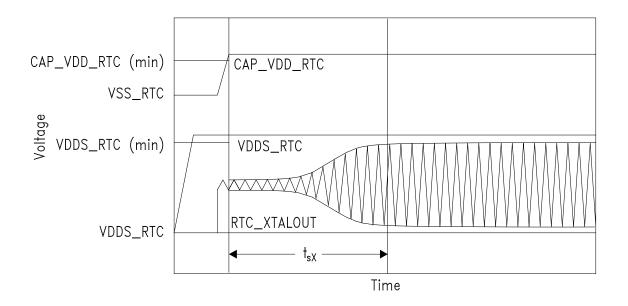

- 3.5.15 <u>OSC1 Start-Up Time</u>. The OSC1 Start-Up Time shall be as shown in figure 15.

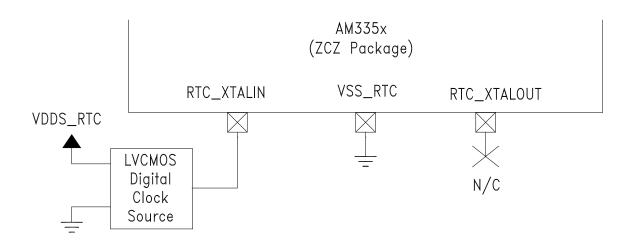

- 3.5.16 OSC1 LVCMOS Circuit Schematic. The OSC1 LVCMOS Circuit Schematic shall be as shown in figure 16.

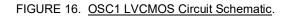

- 3.5.17 <u>DCANx Timings</u>. The DCANx Timings shall be as shown in figure 17.

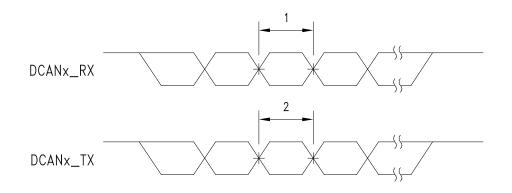

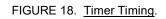

- 3.5.18 <u>Timer Timing</u>. The Timer Timing shall be as shown in figure 18.

- 3.5.19 <u>MDIO DATA Timing Input Mode</u>. The MDIO\_DATA Timing Input Mode shall be as shown in figure 19.

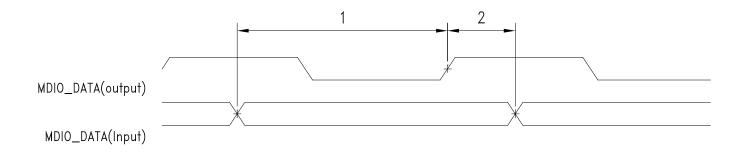

- 3.5.20 MDIO\_CLK Timing. The MDIO\_CLK Timing shall be as shown in figure 20.

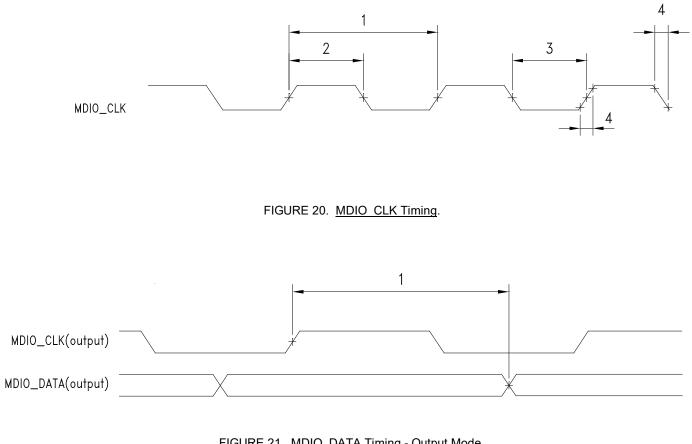

- 3.5.21 MDIO DATA Timing Output Mode. The MDIO\_DATA Timing Output Mode shall be as shown in figure 21.

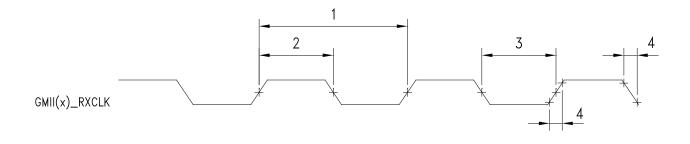

- 3.5.22 <u>GMII[x] RXCLK Timing MII Mode</u>. The GMII[x] RXCLK Timing MII Mode shall be as shown in figure 22.

- 3.5.23 <u>GMII[x] TXCLK Timing MII Mode</u>. The GMII[x]\_TXCLK Timing MII Mode shall be as shown in figure 23.

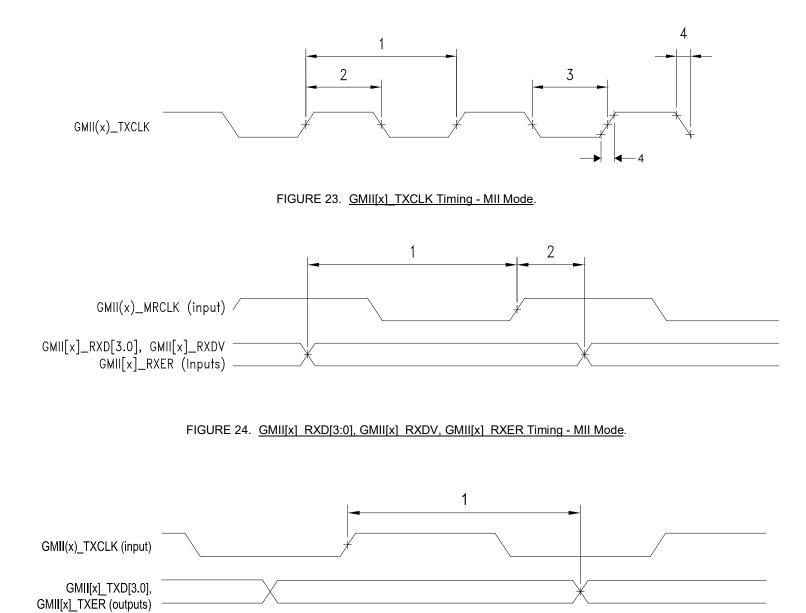

- 3.5.24 <u>GMII[x] RXD[3:0], GMII[x] RXDV, GMII[x] RXER Timing MII Mode</u>. The GMII[x]\_RXD[3:0], GMII[x]\_RXDV, GMII[x]\_RXER Timing MII Mode shall be as shown in figure 24.

- 3.5.25 <u>GMII[x] TXD[3:0], GMII[x] TXEN Timing MII Mode</u>. The GMII[x]\_TXD[3:0], GMII[x]\_TXEN Timing MII Mode shall be as shown in figure 25.

- 3.5.26 RMII[x] REFCLK Timing RMII Mode. The RMII[x]\_REFCLK Timing RMII Mode shall be as shown in figure 26.

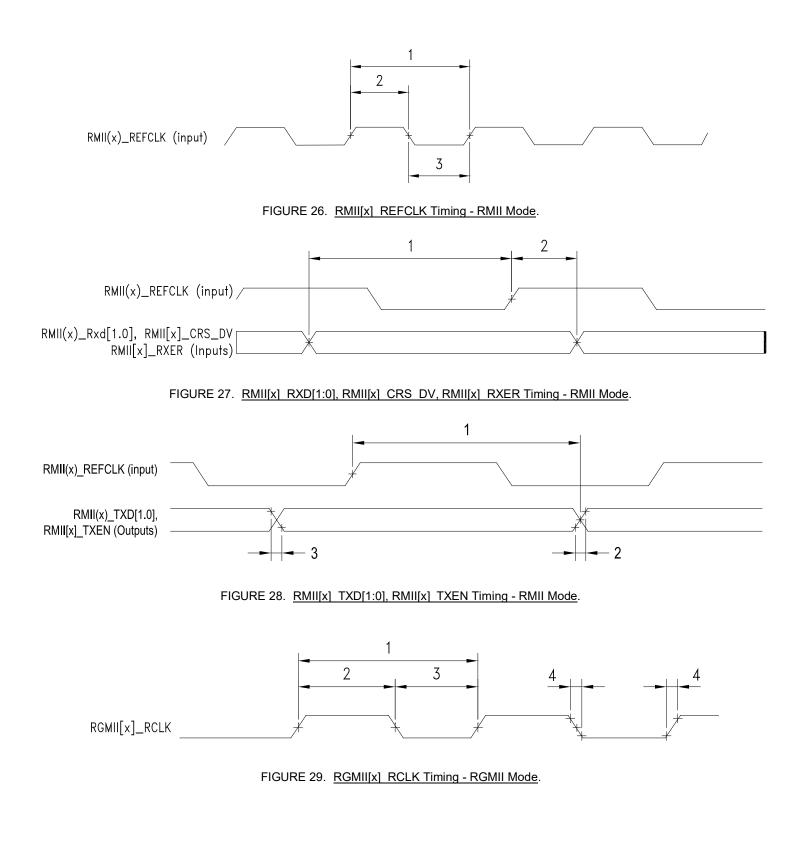

- 3.5.27 <u>RMII[x]\_RXD[1:0], RMII[x]\_CRS\_DV, RMII[x]\_RXER Timing RMII Mode</u>. The RMII[x]\_RXD[1:0], RMII[x]\_CRS\_DV, RMII[x]\_RXER Timing RMII Mode shall be as shown in figure 27.

- 3.5.28 <u>RMII[x] TXD[1:0], RMII[x] TXEN Timing RMII Mode</u>. The RMII[x]\_TXD[1:0], RMII[x]\_TXEN Timing RMII Mode shall be as shown in figure 28.

- 3.5.29 <u>RGMII[x] RCLK Timing RGMII Mode</u>. The RGMII[x]\_RCLK Timing RGMII Mode shall be as shown in figure 29.

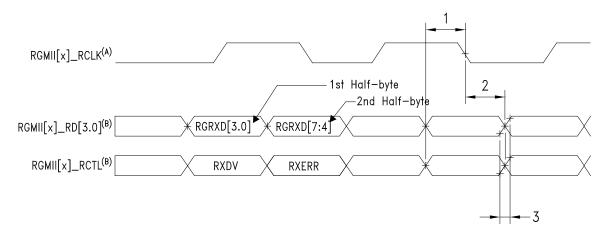

- 3.5.30 <u>RGMII[x]</u> RD[3:0], RGMII[x] RCTL Timing RGMII Mode. The RGMII[x]\_RD[3:0], RGMII[x]\_RCTL Timing RGMII Mode shall be as shown in figure 30.

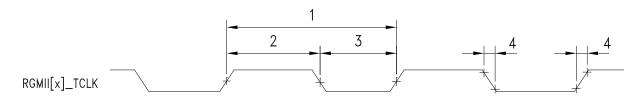

- 3.5.31 <u>RGMII[x]\_TCLK Timing RGMII Mode</u>. The RGMII[x]\_TCLK Timing RGMII Mode shall be as shown in figure 31.

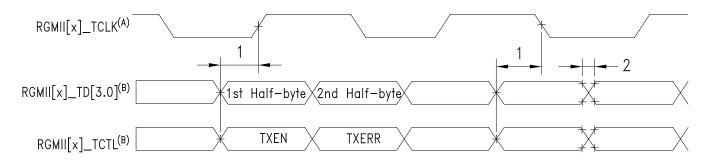

- 3.5.32 <u>RGMII[x]</u> TD[3:0], <u>RGMII[x]</u> TCTL Timing <u>RGMII Mode</u>. The RGMII[x]\_TD[3:0], <u>RGMII[x]\_TCTL</u> Timing <u>RGMII Mode</u> shall be as shown in figure 32.

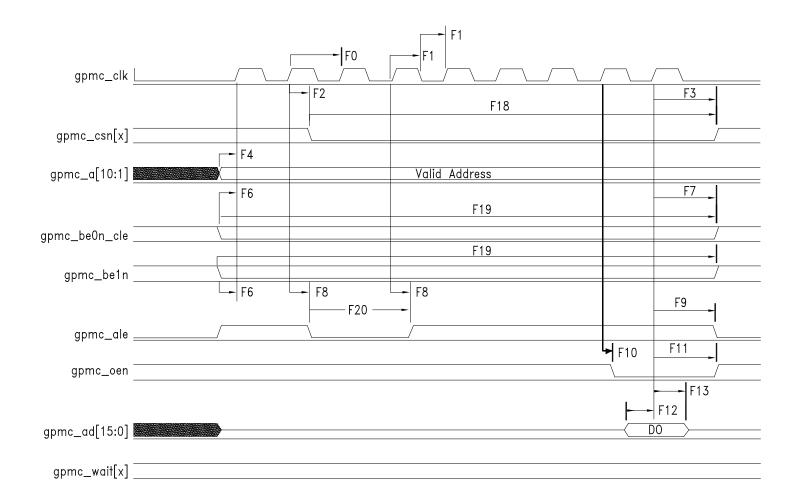

- 3.5.33 <u>GPMC and NOR Flash—Synchronous Single Read—(GpmcFCLKDivider = 0)</u>. The GPMC and NOR Flash—Synchronous Single Read—(GpmcFCLKDivider = 0) shall be as shown in figure 33.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV A          | PAGE 11                  |

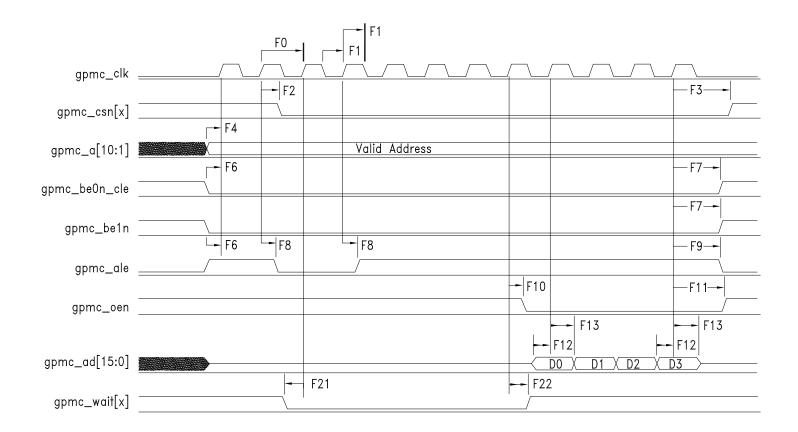

- 3.5.34 <u>GPMC and NOR Flash—Synchronous Burst Read—4x16-bit (GpmcFCLKDivider = 0)</u>. The GPMC and NOR Flash— Synchronous Burst Read—4x16-bit (GpmcFCLKDivider = 0) shall be as shown in figure 34.

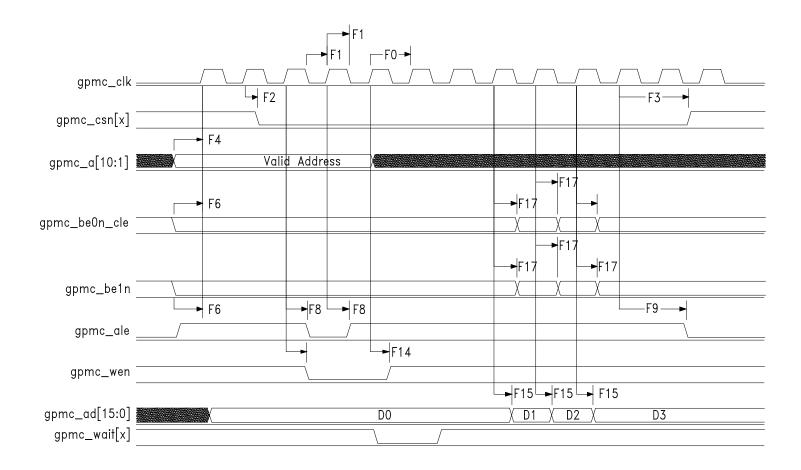

- 3.5.35 <u>GPMC and NOR Flash—Synchronous Burst Write—(GpmcFCLKDivider > 0)</u>. The GPMC and NOR Flash—Synchronous Burst Write—(GpmcFCLKDivider > 0) shall be as shown in figure 35.

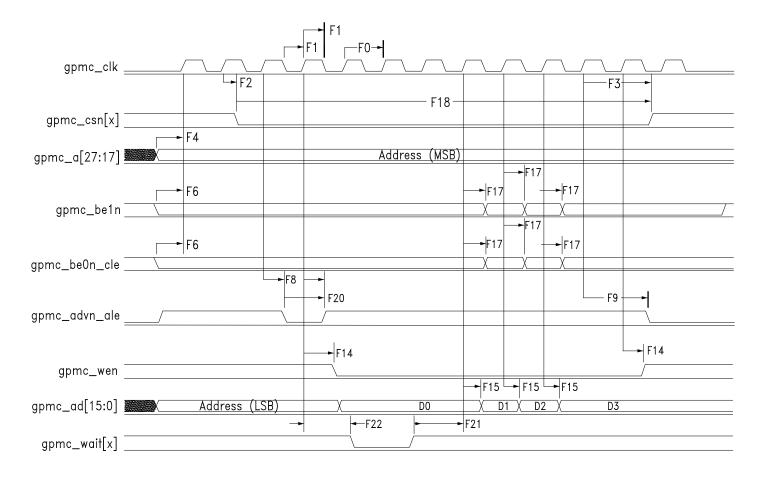

- 3.5.36 <u>GPMC and Multiplexed NOR Flash—Synchronous Burst Read</u>. The GPMC and Multiplexed NOR Flash—Synchronous Burst Read shall be as shown in figure 36.

- 3.5.37 <u>GPMC and Multiplexed NOR Flash—Synchronous Burst Write</u>. The GPMC and Multiplexed NOR Flash—Synchronous Burst Write shall be as shown in figure 37.

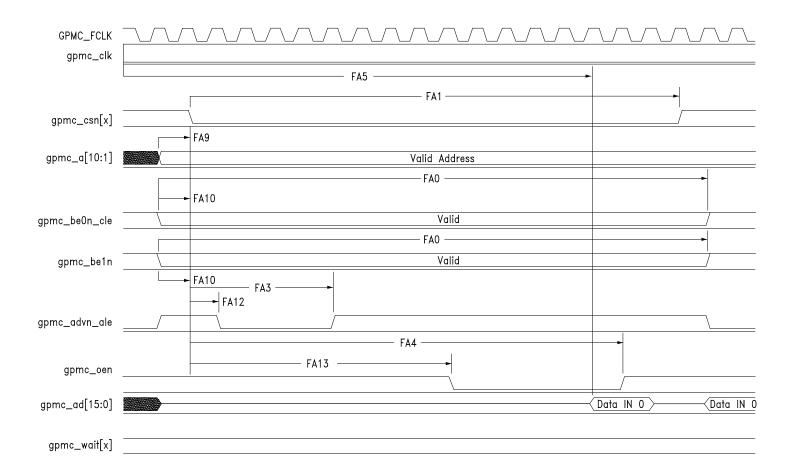

- 3.5.38 <u>GPMC and NOR Flash—Asynchronous Read—Single Word</u>. The GPMC and NOR Flash—Asynchronous Read—Single Word shall be as shown in figure 38.

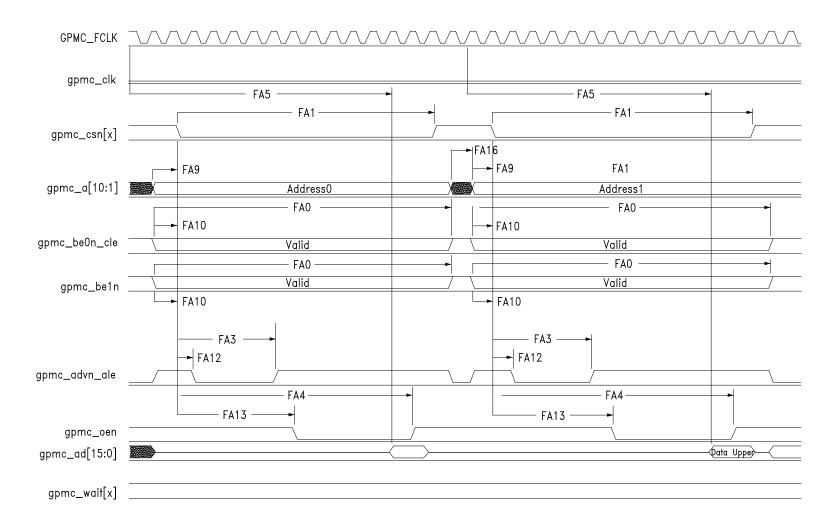

- 3.5.39 <u>GPMC and NOR Flash—Asynchronous Read—32-bit</u>. The <u>GPMC and NOR Flash—Asynchronous Read—32-bit</u> shall be as shown in figure 39.

- 3.5.40 <u>GPMC and NOR Flash—Asynchronous Read—Page Mode 4x16-bit</u>. The GPMC and NOR Flash—Asynchronous Read— Page Mode 4x16-bit shall be as shown in figure 40.

- 3.5.41 <u>GPMC and NOR Flash—Asynchronous Write—Single Word</u>. The GPMC and NOR Flash—Asynchronous Write—Single Word shall be as shown in figure 41.

- 3.5.42 <u>GPMC and Multiplexed NOR Flash—Asynchronous Read—Single Word</u>. The GPMC and Multiplexed NOR Flash— Asynchronous Read—Single Word shall be as shown in figure 42.

- 3.5.43 <u>GPMC and Multiplexed NOR Flash—Asynchronous Write—Single Word</u>. The GPMC and Multiplexed NOR Flash— Asynchronous Write—Single Word shall be as shown in figure 43.

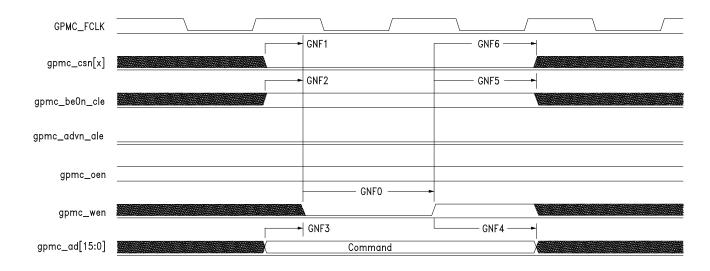

- 3.5.44 <u>GPMC and NAND Flash—Command Latch Cycle</u>. The GPMC and NAND Flash—Command Latch Cycle shall be as shown in figure 44.

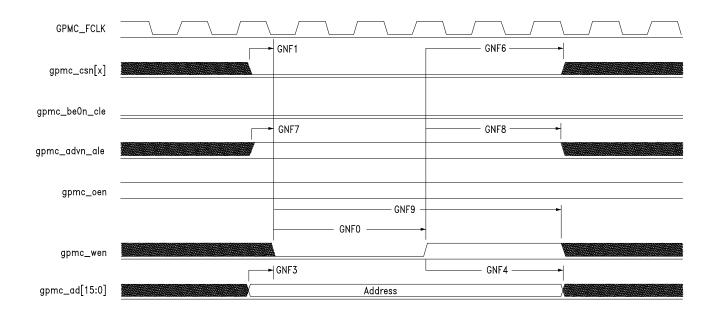

- 3.5.45 <u>GPMC and NAND Flash—Address Latch Cycle</u>. The GPMC and NAND Flash—Address Latch Cycle shall be as shown in figure 45.

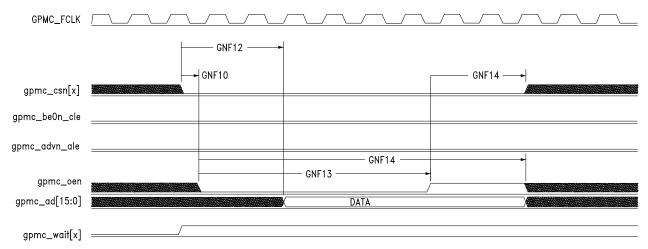

- 3.5.46 <u>GPMC and NAND Flash—Data Read Cycle</u>. The GPMC and NAND Flash—Data Read Cycle shall be as shown in figure 46.

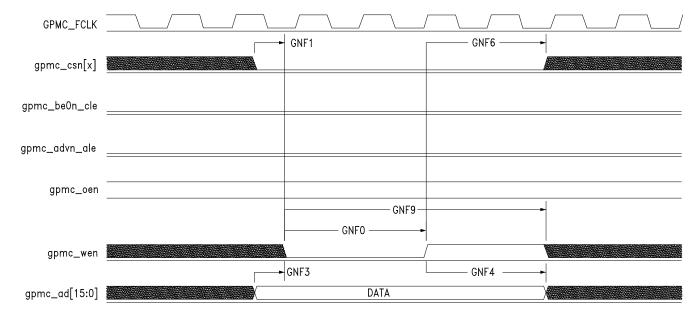

- 3.5.47 <u>GPMC and NAND Flash— Data Write Cycle</u>. The GPMC and NAND Flash— Data Write Cycle shall be as shown in figure

47.

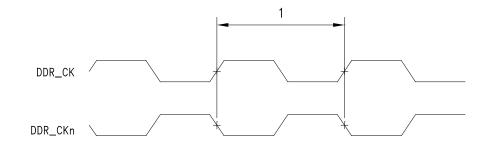

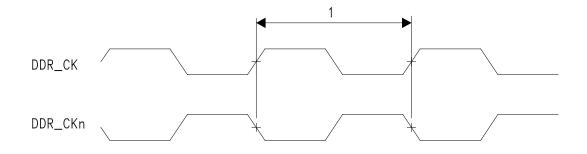

- 3.5.48 <u>LPDDR Memory Interface Clock Timing</u>. The LPDDR Memory Interface Clock Timing shall be as shown in figure 48.

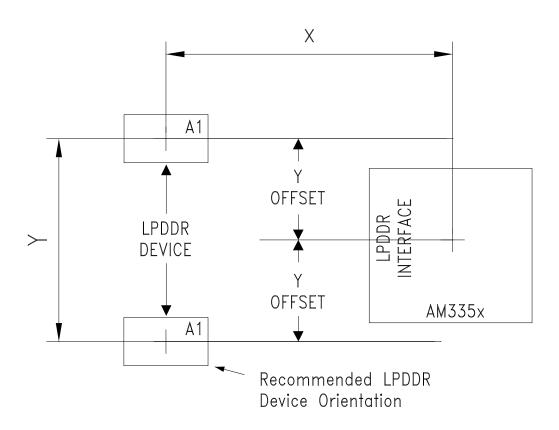

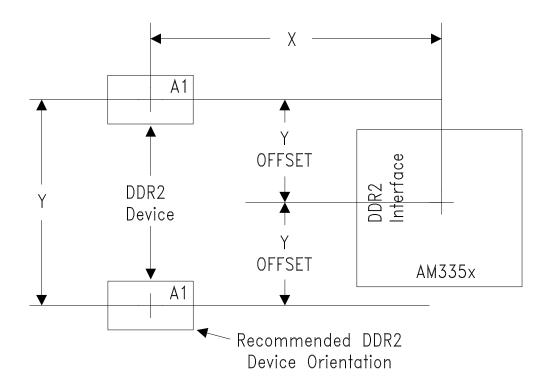

- 3.5.49 <u>AM3358-EP Device and LPDDR Device Placement</u>. The AM3358-EP Device and LPDDR Device Placement shall be as shown in figure 49.

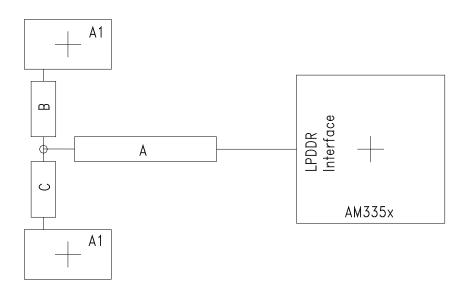

- 3.5.50 <u>CK and ADDR\_CTRL Routing and Topology</u>. The CK and ADDR\_CTRL Routing and Topology shall be as shown in figure 50.

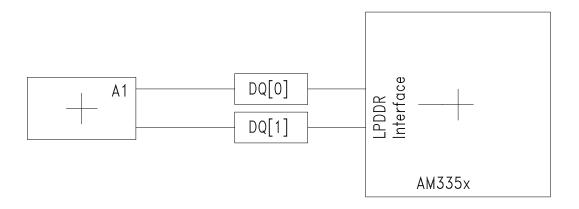

- 3.5.51 <u>DQS[x] and DQ[x] Routing and Topology</u>. The DQS[x] and DQ[x] Routing and Topology shall be as shown in figure 51.

- 3.5.52 DDR2 Memory Interface Clock Timing. The DDR2 Memory Interface Clock Timing shall be as shown in figure 52.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV A          | PAGE 12                  |

- 3.5.53 <u>AM3358-EP Device and DDR2 Device Placement</u>. The AM3358-EP Device and DDR2 Device Placement shall be as shown in figure 53.

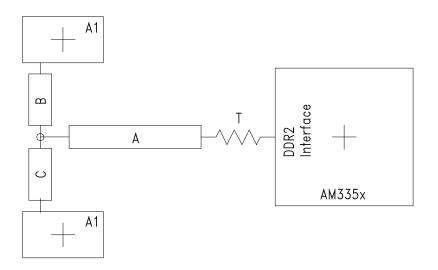

- 3.5.54 <u>CK and ADDR\_CTRL Routing and Topology</u>. The CK and ADDR\_CTRL Routing and Topology shall be as shown in figure 54.

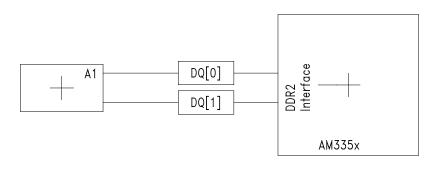

- 3.5.55 <u>DQS[x] and DQ[x] Routing and Topology</u>. The DQS[x] and DQ[x] Routing and Topology shall be as shown in figure 55.

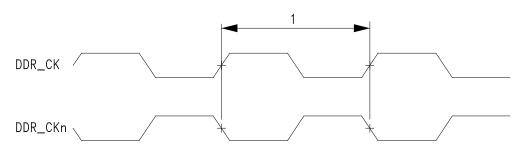

- 3.5.56 <u>DDR3 Memory Interface Clock Timing</u>. The DDR3 Memory Interface Clock Timing shall be as shown in figure 56.

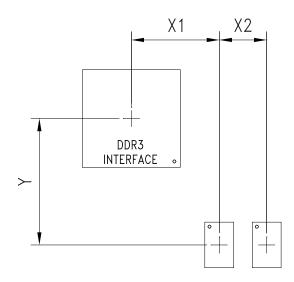

- 3.5.57 <u>Placement Specifications</u>. The Placement Specifications shall be as shown in figure 57.

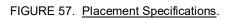

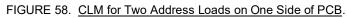

- 3.5.58 <u>CLM for Two Address Loads on One Side of PCB</u>. The CLM for Two Address Loads on One Side of PCB shall be as shown in figure 58.

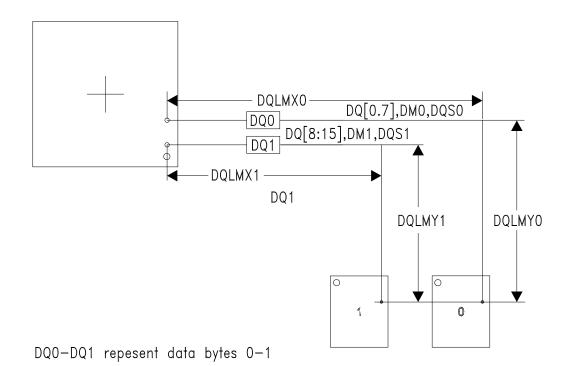

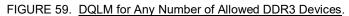

- 3.5.59 DQLM for Any Number of Allowed DDR3 Devices. The DQLM for Any Number of Allowed DDR3 Devices shall be as shown in figure 59.

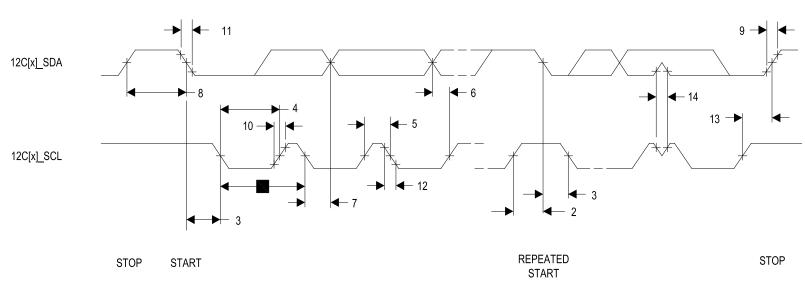

- 3.5.60 <u>I<sup>2</sup>C Receive Timing</u>. The I<sup>2</sup>C Receive Timing shall be as shown in figure 60.

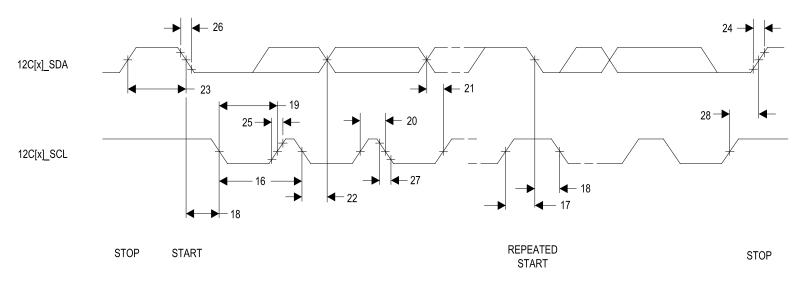

- 3.5.61 <u>I<sup>2</sup>C Transmit Timing</u>. The I<sup>2</sup>C Transmit Timing shall be as shown in figure 61.

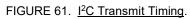

- 3.5.62 JTAG Timing. The JTAG Timing shall be as shown in figure 62.

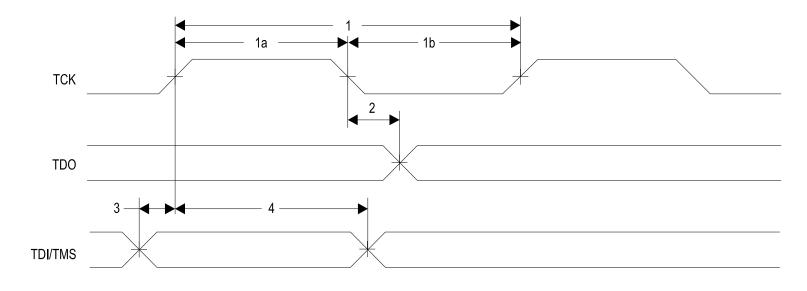

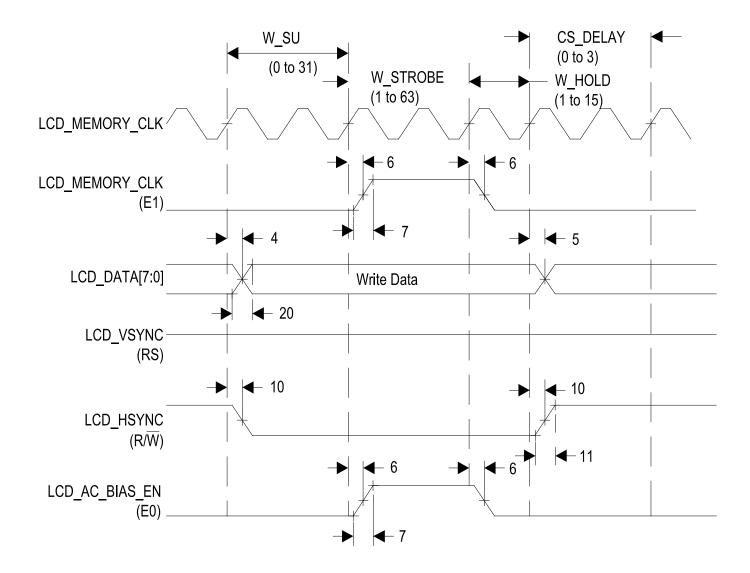

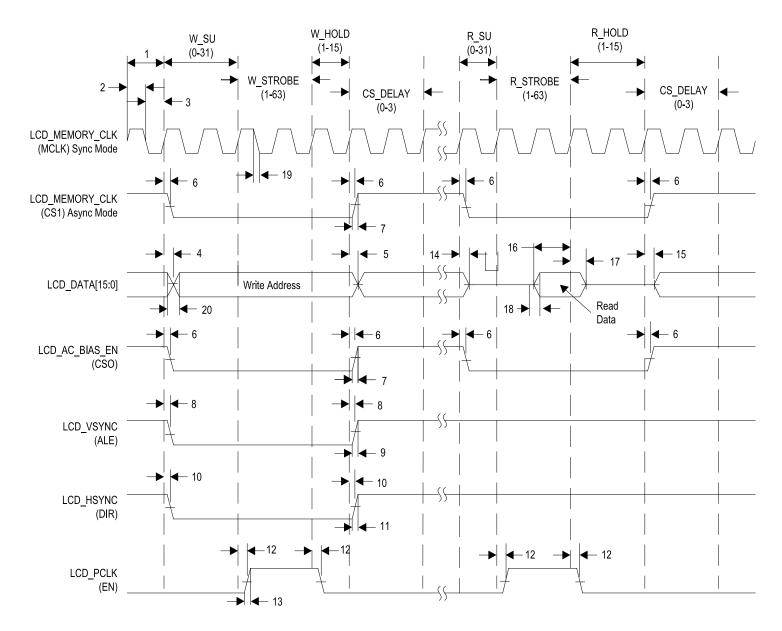

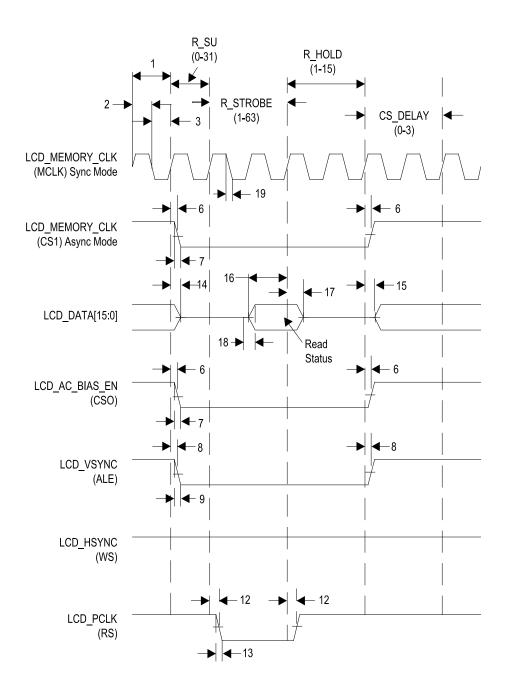

- 3.5.63 <u>Command Write in Hitachi Mode</u>. The Command Write in Hitachi Mode shall be as shown in figure 63.

- 3.5.64 <u>Data Write in Hitachi Mode</u>. The Data Write in Hitachi Mode shall be as shown in figure 64.

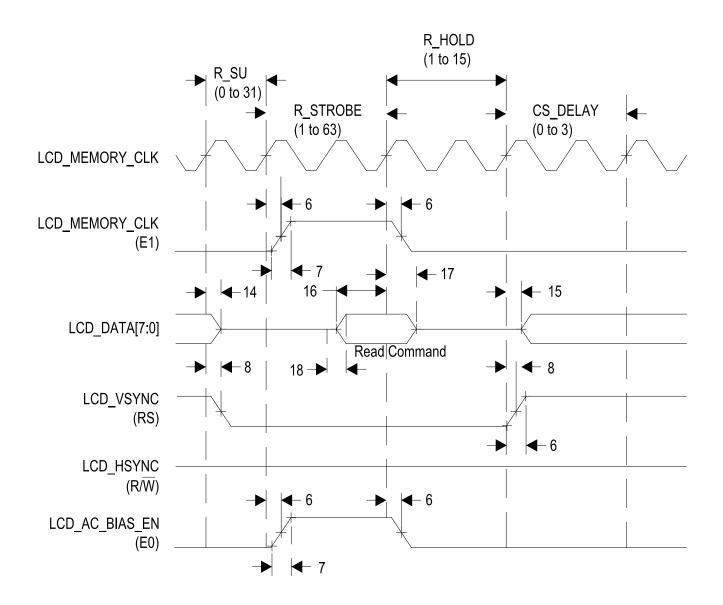

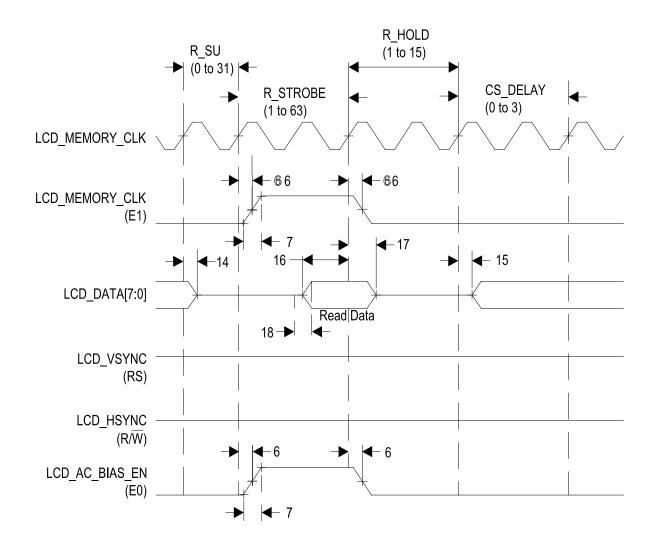

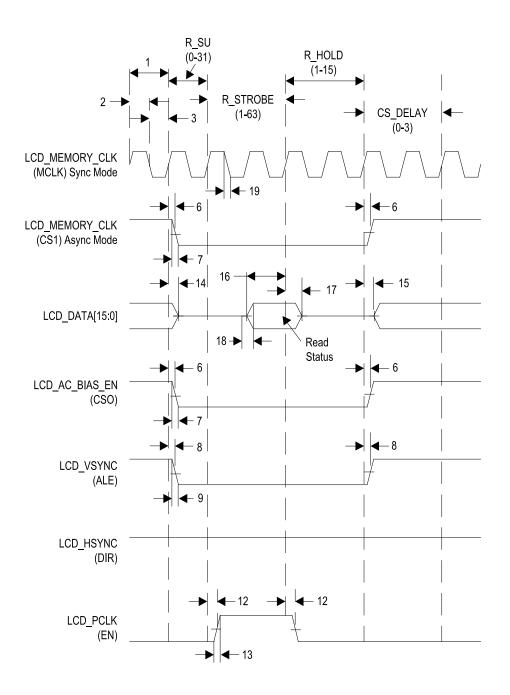

- 3.5.65 <u>Command Read in Hitachi Mode</u>. The Command Read in Hitachi Mode shall be as shown in figure 65.

- 3.5.66 <u>Data Read in Hitachi Mode</u>. The Data Read in Hitachi Mode shall be as shown in figure 66.

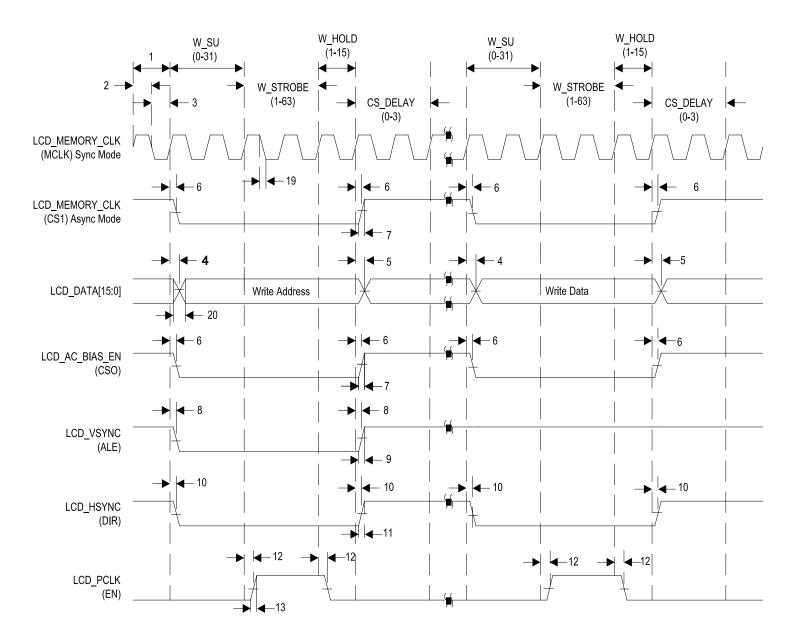

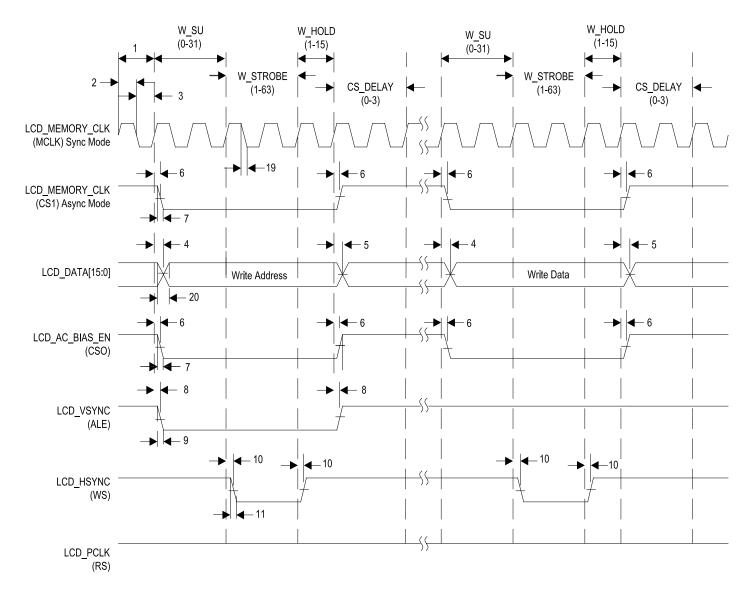

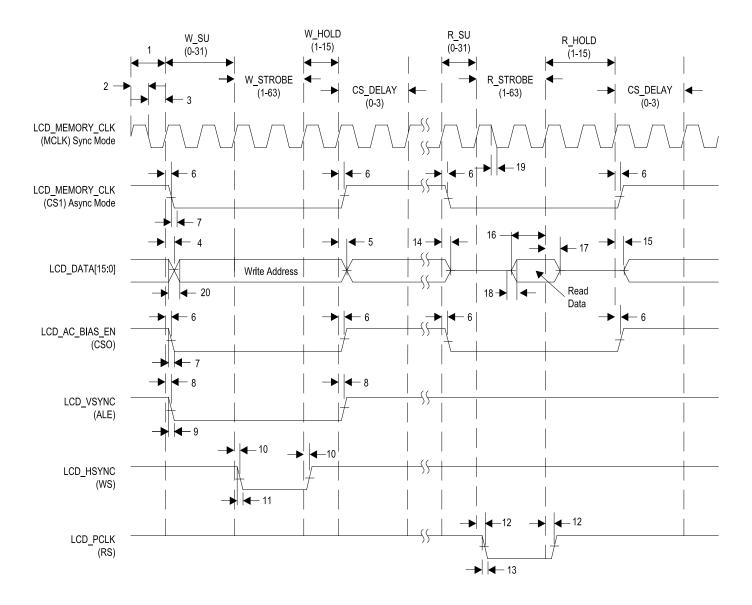

- 3.5.67 <u>Micro-Interface Graphic Display Motorola Write</u>. The Micro-Interface Graphic Display Motorola Write shall be as shown in figure 67.

- 3.5.68 <u>Micro-Interface Graphic Display Motorola Read</u>. The Micro-Interface Graphic Display Motorola Read shall be as shown in figure 68.

- 3.5.69 <u>Micro-Interface Graphic Display Motorola Status</u>. The Micro-Interface Graphic Display Motorola Status shall be as shown in figure 69.

- 3.5.70 <u>Micro-Interface Graphic Display Intel Write</u>. The Micro-Interface Graphic Display Intel Write shall be as shown in figure 70.

- 3.5.71 Micro-Interface Graphic Display Intel Read. The Micro-Interface Graphic Display Intel Read shall be as shown in figure 71.

- 3.5.72 Micro-Interface Graphic Display Intel Status. The Micro-Interface Graphic Display Intel Status shall be as shown in figure 72.

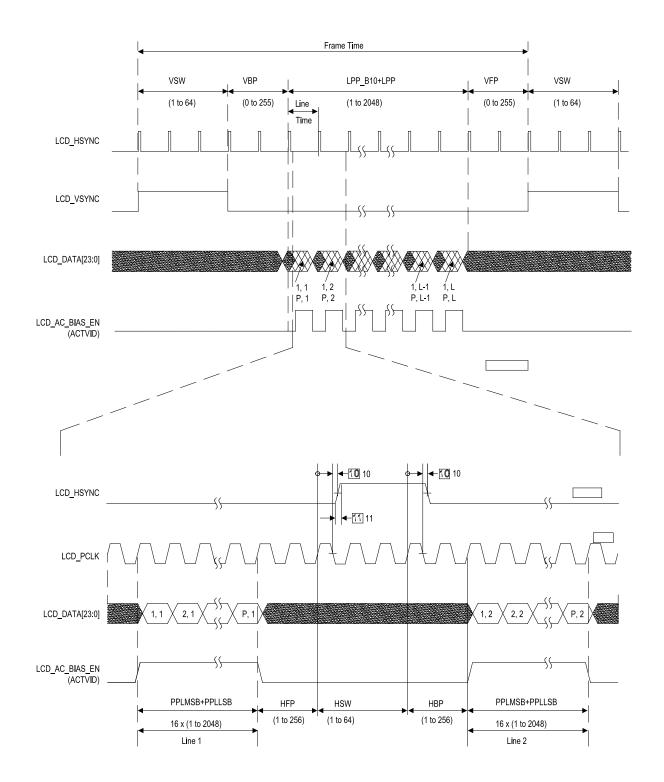

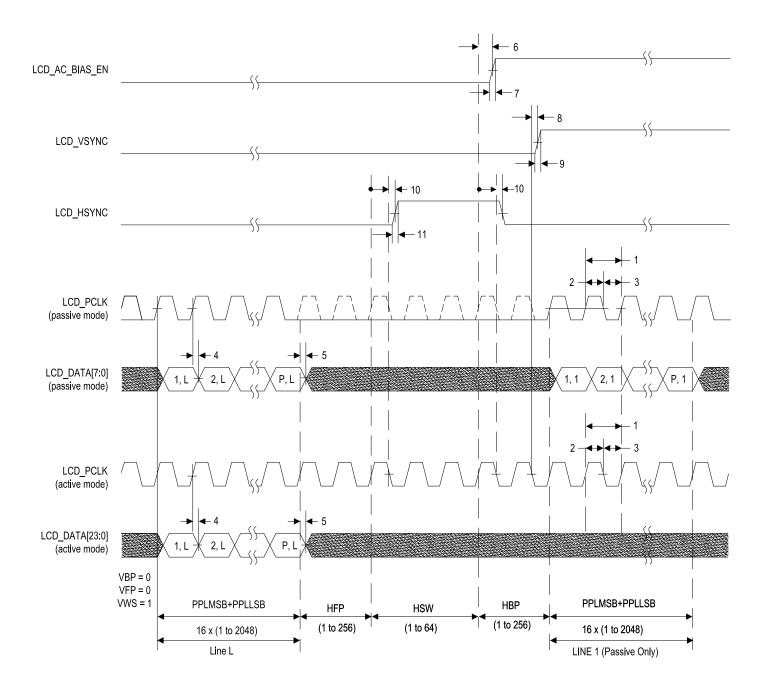

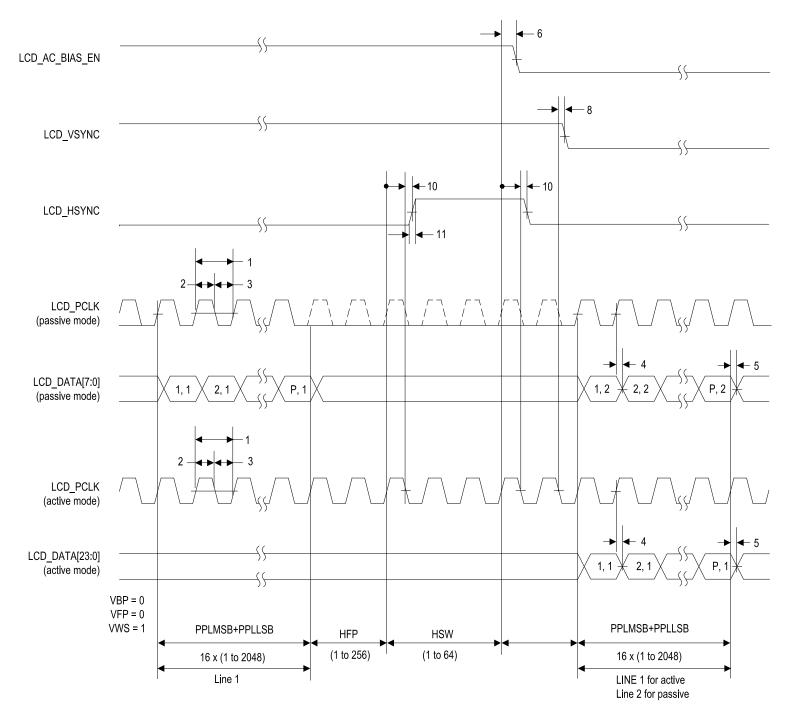

- 3.5.73 <u>LCD Raster-Mode Active</u>. The LCD Raster-Mode Active shall be as shown in figure 73.

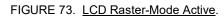

- 3.5.74 LCD Raster-Mode Passive. The LCD Raster-Mode Passive shall be as shown in figure 74.

- 3.5.75 <u>LCD Raster-Mode Control Signal Activation</u>. The LCD Raster-Mode Control Signal Activation shall be as shown in figure 75.

- 3.5.76 <u>LCD Raster-Mode Control Signal Deactivation</u>. The LCD Raster-Mode Control Signal Deactivation shall be as shown in figure 76.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV A          | PAGE 13                  |

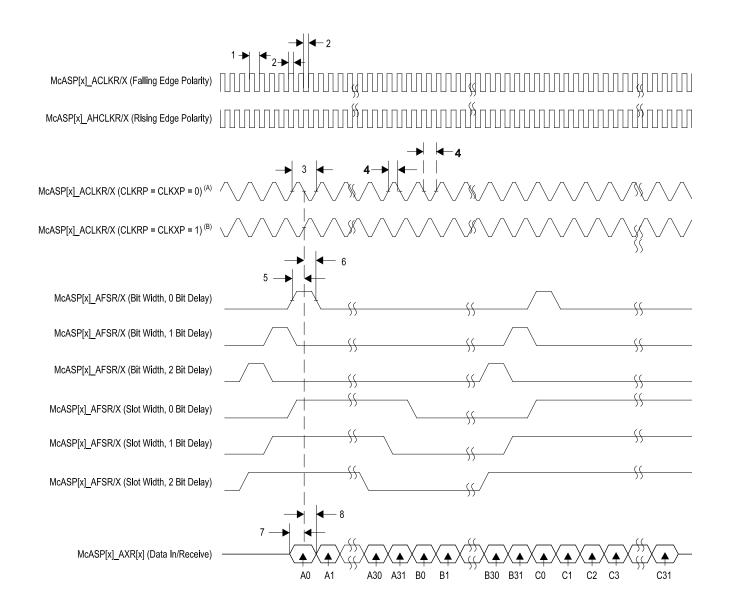

- 3.5.77 McASP Input Timing. The McASP Input Timing shall be as shown in figure 77.

- 3.5.78 McASP Input Timing. The McASP Input Timing shall be as shown in figure 78.

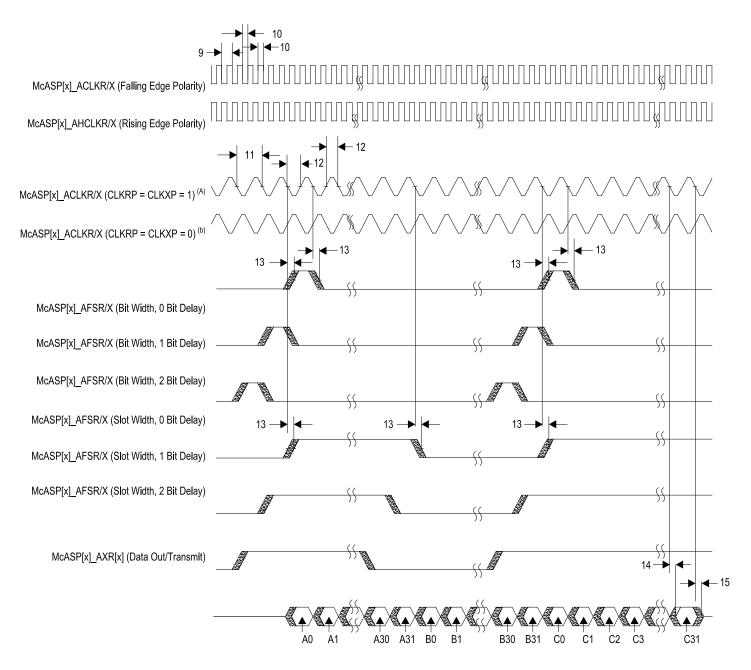

- 3.5.79 McASP Output Timing. The McASP Output Timing shall be as shown in figure 79.

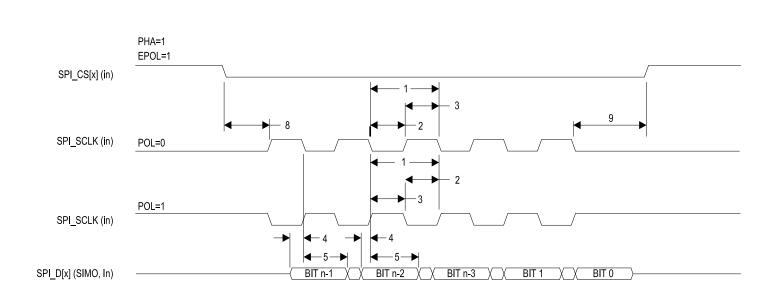

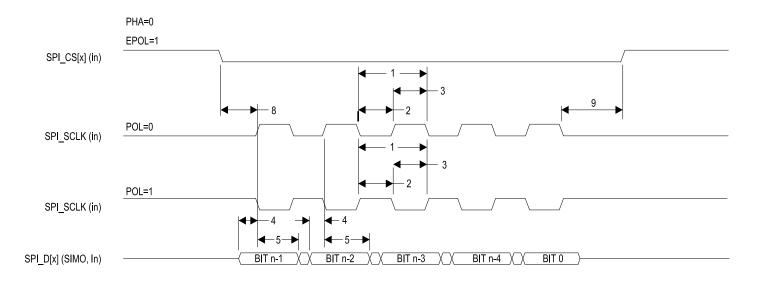

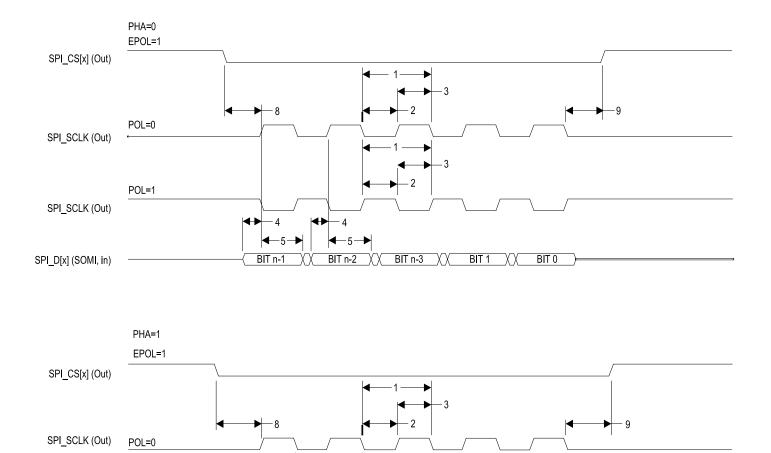

- 3.5.80 <u>SPI Slave Mode Receive Timing</u>. The SPI Slave Mode Receive Timing shall be as shown in figure 80.

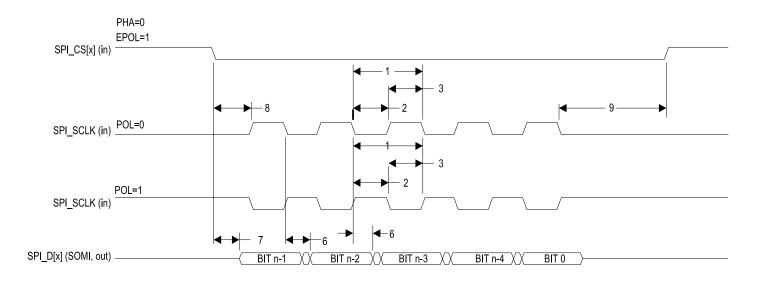

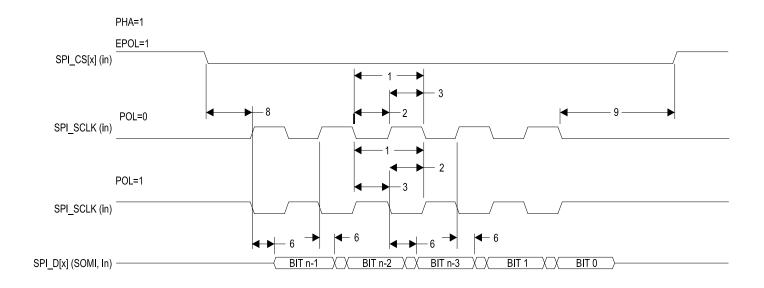

- 3.5.81 <u>SPI Slave Mode Transmit Timing</u>. The SPI Slave Mode Transmit Timing shall be as shown in figure 81.

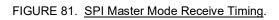

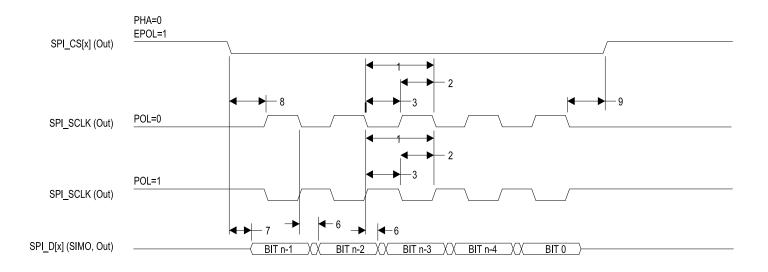

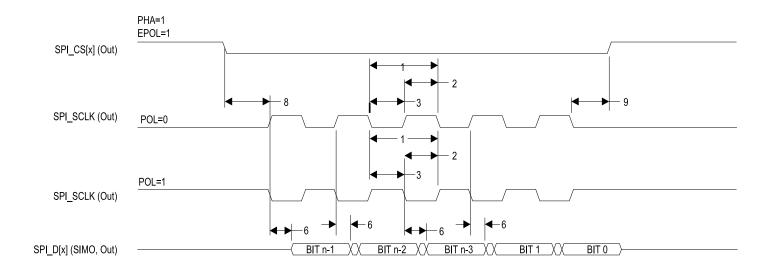

- 3.5.82 <u>SPI Master Mode Receive Timing</u>. The SPI Master Mode Receive Timing shall be as shown in figure 82.

- 3.5.83 <u>SPI Master Mode Transmit Timing</u>. The SPI Master Mode Transmit Timing shall be as shown in figure 83.

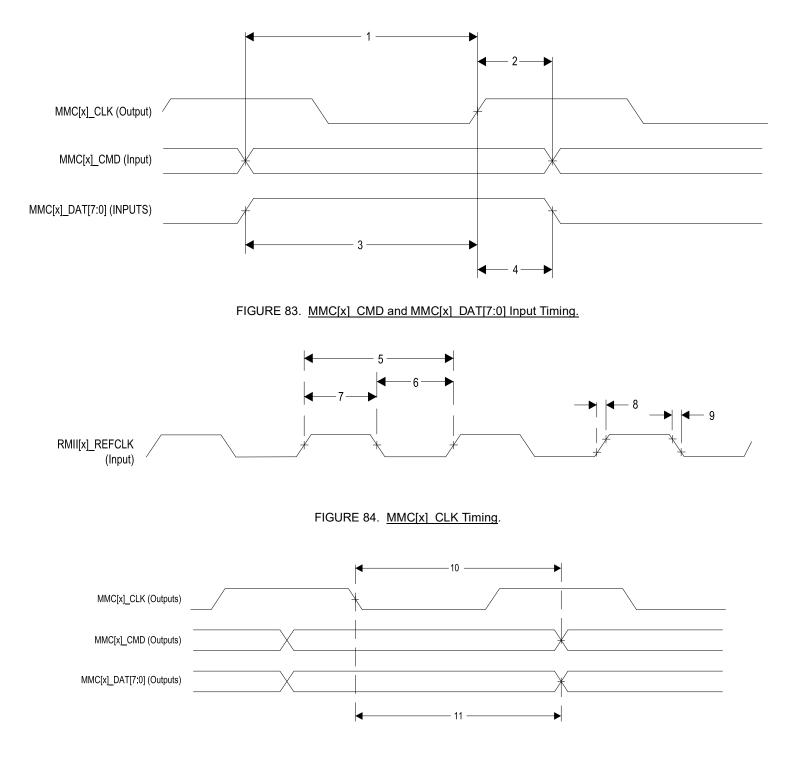

- 3.5.84 <u>MMC[x] CMD and MMC[x] DAT[7:0] Input Timing</u>. The MMC[x]\_CMD and MMC[x]\_DAT[7:0] Input Timing shall be as shown in figure 84.

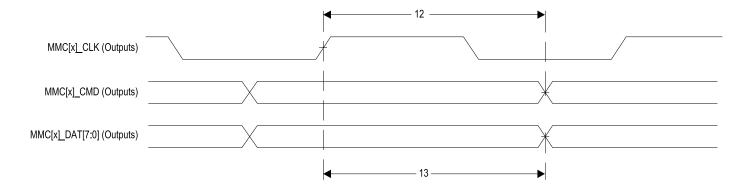

- 3.5.85 <u>MMC[x]\_CMD and MMC[x]\_DAT[7:0] Output Timing—Standard Mode</u>. The MMC[x]\_CMD and MMC[x]\_DAT[7:0] Output Timing—Standard Mode shall be as shown in figure 85.

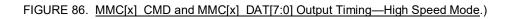

- 3.5.86 <u>MMC[x] CMD and MMC[x] DAT[7:0] Output Timing—High Speed Mode</u>. The MMC[x]\_CMD and MMC[x]\_DAT[7:0] Output Timing—High Speed Mode shall be as shown in figure 86.

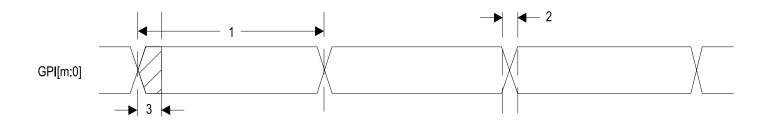

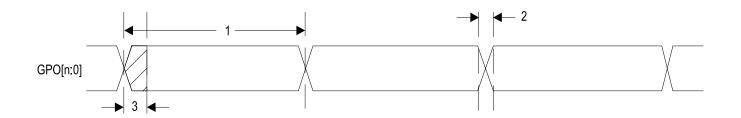

- 3.5.87 <u>PRU-ICSS PRU Direct Input Timing</u>. The PRU-ICSS PRU Direct Input Timing shall be as shown in figure 87.

- 3.5.88 <u>PRU-ICSS PRU Direct Output Timing</u>. The PRU-ICSS PRU Direct Output Timing shall be as shown in figure 88.

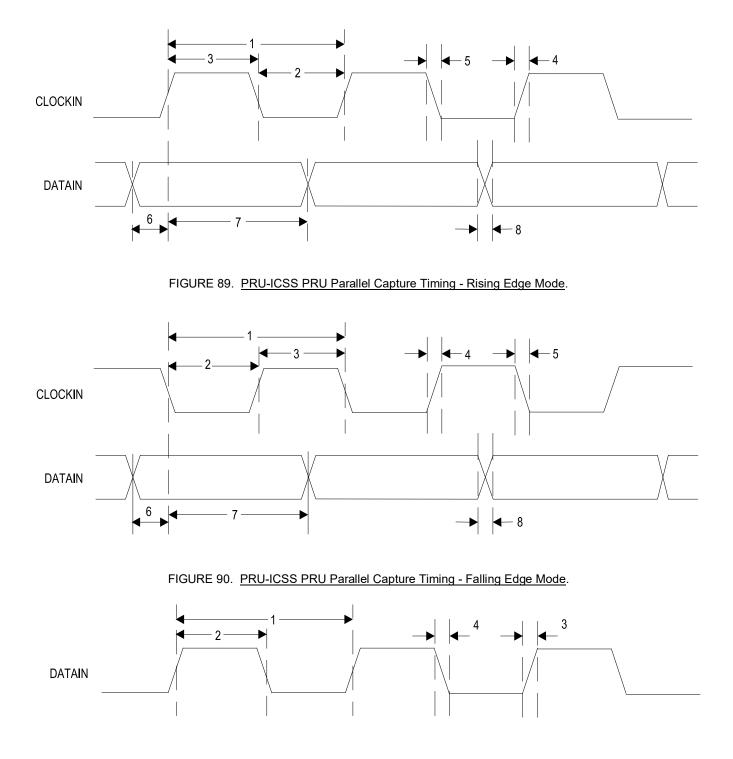

- 3.5.89 <u>PRU-ICSS PRU Parallel Capture Timing Rising Edge Mode</u>. The PRU-ICSS PRU Parallel Capture Timing Rising Edge Mode shall be as shown in figure 89.

- 3.5.90 <u>PRU-ICSS PRU Parallel Capture Timing Falling Edge Mode</u>. The PRU-ICSS PRU Parallel Capture Timing Falling Edge Mode shall be as shown in figure 90.

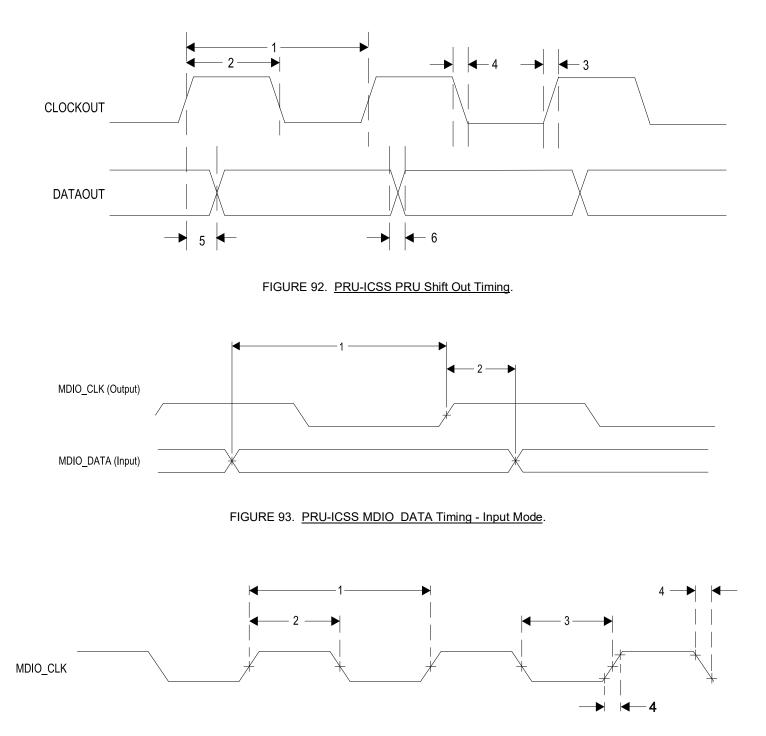

- 3.5.91 PRU-ICSS PRU Shift In Timing. The PRU-ICSS PRU Shift In Timing shall be as shown in figure 91.

- 3.5.92 PRU-ICSS PRU Shift Out Timing. The PRU-ICSS PRU Shift Out Timing shall be as shown in figure 92.

- 3.5.93 <u>PRU-ICSS MDIO\_DATA Timing Input Mode</u>. The PRU-ICSS MDIO\_DATA Timing Input Mode shall be as shown in figure 93.

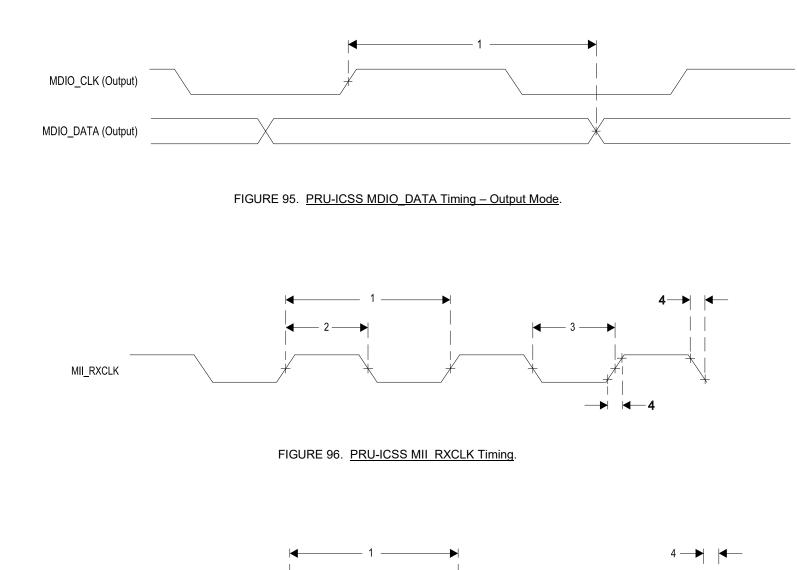

- 3.5.94 <u>PRU-ICSS MDIO\_CLK Timing</u>. The PRU-ICSS MDIO\_CLK Timing shall be as shown in figure 94.

- 3.5.95 <u>PRU-ICSS MDIO\_DATA Timing Output Mode</u>. The PRU-ICSS MDIO\_DATA Timing Output Mode shall be as shown in figure 95.

- 3.5.96 <u>PRU-ICSS MII\_RXCLK Timing</u>. The PRU-ICSS MII\_RXCLK Timing shall be as shown in figure 96.

- 3.5.97 <u>PRU-ICSS MII\_TXCLK Timing</u>. The PRU-ICSS MII\_TXCLK Timing shall be as shown in figure 97.

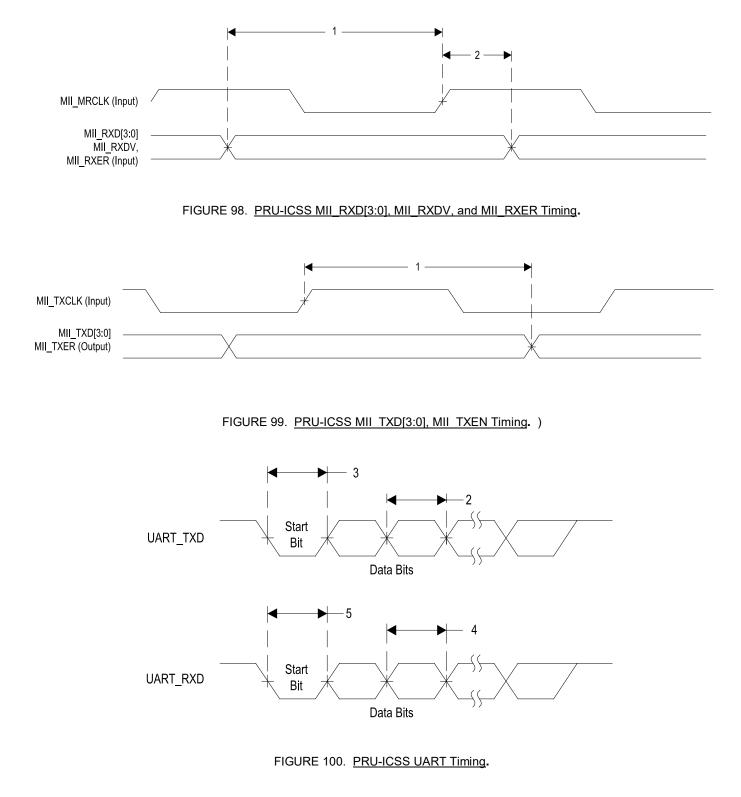

- 3.5.98 <u>PRU-ICSS MII\_RXD[3:0], MII\_RXDV, and MII\_RXER Timing</u>. The PRU-ICSS MII\_RXD[3:0], MII\_RXDV, and MII\_RXER Timing shall be as shown in figure 98.

- 3.5.99 <u>PRU-ICSS MII\_TXD[3:0], MII\_TXEN Timing</u>. The PRU-ICSS MII\_TXD[3:0], MII\_TXEN Timing shall be as shown in figure 99.

- 3.5.100 <u>PRU-ICSS UART Timing</u>. The PRU-ICSS UART Timing shall be as shown in figure 100.

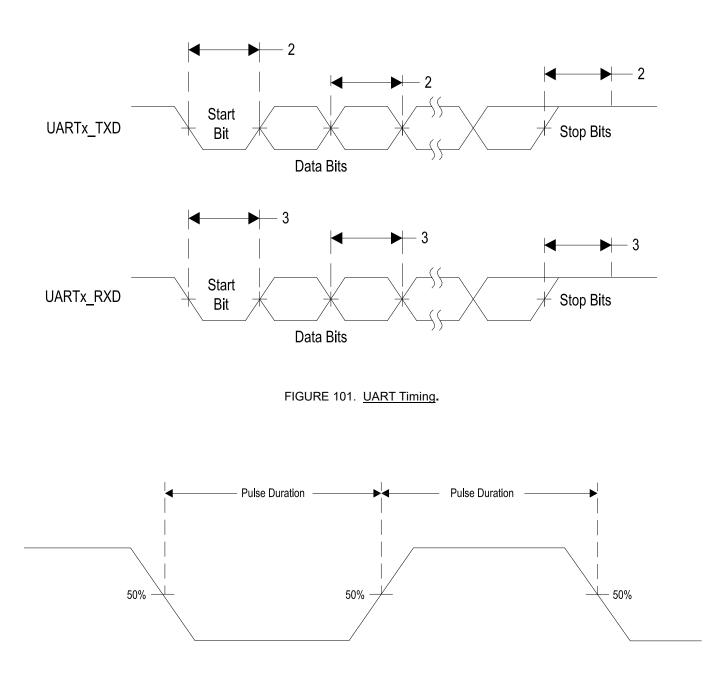

- 3.5.101 <u>UART Timing</u>. The UART Timing shall be as shown in figure 101.

- 3.5.102 <u>UART IrDA Pulse Parameters</u>. The UART IrDA Pulse Parameters shall be as shown in figure 102.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV A          | PAGE 14                  |

# TABLE I. Electrical performance characteristics. 1/ 2/ 3/

| Test                                                                                                                                                                                                     |                                | Symbol                       | Limits                                |                     |                           | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------|---------------------------------------|---------------------|---------------------------|------|

|                                                                                                                                                                                                          |                                |                              | Min                                   | Тур                 | Max                       |      |

| DC Electrical Characteristics <u>3/</u>                                                                                                                                                                  |                                |                              |                                       |                     |                           |      |

| DDR_RESETn,DDR_CSn0,DDR_CKE,DDR_CK,DD<br>DDR_A0,DDR_A1,DDR_A2,DDR_A3,DDR_A4,DDR<br>DDR_A13,DDR_A14,DDR_A15,DDR_ODT,DDR_D0<br>DDR_D9,DDR_D10, DDR_D11,DDR_D12,DDR_D1<br>DDR_DQSn0,DDR_DQS1,DDR_DQSn1 Pins | 2_A5,DDR_A6,D<br>),DDR_D1,DDR_ | DR_A7,DDR_A8<br>_D2,DDR_D3,D | 8,DDR_A9,DDR_A10,<br>DR_D4,DDR_D5,DDF | DDR_A11<br>R_D6,DDR | ,DDR_A12,<br>R_D7,DDR_D8, |      |

| High-level input voltage                                                                                                                                                                                 |                                | Vih                          | 0.65 × VDDS_DDR                       |                     |                           | V    |

| Low-level input voltage                                                                                                                                                                                  |                                | VIL                          |                                       |                     | 0.35 ×<br>VDDS_DDR        | V    |

| Hysteresis voltage at an input                                                                                                                                                                           | V <sub>HYS</sub>               | 0.07                         |                                       | 0.25                | V                         |      |

| High level output voltage, driver enabled, pullup or<br>pulldown disabled                                                                                                                                |                                | Vон                          | VDDS_DDR – 0.4                        |                     |                           | V    |

| Low level output voltage, driver enabled, pullup<br>orpulldown disabled                                                                                                                                  | I <sub>OL</sub> = 8 mA         | Vol                          |                                       |                     | 0.4                       | V    |

| Input leakage current, Receiver disabled, pullup or p<br>inhibited                                                                                                                                       | h                              |                              |                                       | 10                  | μA                        |      |

| Input leakage current, Receiver disabled, pullup ena                                                                                                                                                     |                                | -240                         |                                       | -80                 |                           |      |

| Input leakage current, Receiver disabled, pulldown e                                                                                                                                                     | nabled                         |                              | 80                                    |                     | 240                       |      |

| Total leakage current through the terminal connectio<br>receiver combination that may include a pullup or pu<br>driver output is disabled and the pullup or pulldown                                     | lldown. The                    | loz                          |                                       |                     | 10                        | μA   |

| DDR_A13,DDR_A14,DDR_A15, DDR_ODT,DDR_D<br>DDR_D9,DDR_D10,DDR_D11,DDR_D12,DDR_D13<br>DDR_DQS1,DDR_DQSn1 Pins (DDR2 - SSTL Mod                                                                             | B,DDR_D14, DDI                 |                              | QM0,DDR_DQM1,DDF                      |                     |                           |      |

| High-level input voltage                                                                                                                                                                                 |                                | VIH                          | DDR_VREF +<br>0.125                   |                     |                           | V    |

| Low-level input voltage                                                                                                                                                                                  |                                | VIL                          |                                       |                     | DDR_VREF -<br>0.125       | V    |

| Hysteresis voltage at an input                                                                                                                                                                           | T                              | V <sub>HYS</sub>             |                                       | N/A                 |                           | V    |

| High level output voltage, driver enabled, pullup or pulldown disabled                                                                                                                                   | I <sub>ОН</sub> = 8 mA         | Vон                          | vdds_ddr -<br>0.4                     |                     |                           | V    |

| Low level output voltage, driver enabled, pullup<br>orpulldown disabled                                                                                                                                  | l <sub>o∟</sub> = 8 mA         | Vol                          |                                       |                     | 0.4                       | V    |

| Input leakage current, Receiver disabled, pullup or p<br>inhibited                                                                                                                                       | ulldown                        | lı                           |                                       |                     | 10                        | μA   |

| Input leakage current, Receiver disabled, pullup ena                                                                                                                                                     | bled                           |                              | -240                                  |                     | -80                       |      |

| Input leakage current, Receiver disabled, pulldown e                                                                                                                                                     |                                | 80                           |                                       | 240                 |                           |      |

| Total leakage current through the terminal connectio<br>receiver combination that may include a pullup or pu<br>driver output is disabled and the pullup or pulldown                                     | lldown. The                    | loz                          |                                       |                     | 10                        | μA   |

| See footnote at end of table.                                                                                                                                                                            |                                |                              |                                       |                     |                           | _    |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV A          | PAGE 15                  |

#### TABLE I. Electrical performance characteristics - Continued. 1/ 2/ 3/

| Test | Symbol |     | Limits |     |  |

|------|--------|-----|--------|-----|--|

|      |        | Min | Тур    | Max |  |

#### DC Electrical Characteristics (Continued) <u>3/</u>

DDR\_RESETn,DDR\_CSn0,DDR\_CKE,DDR\_CK,DDR\_CKn,DDR\_CASn,DDR\_RASn,DDR\_WEn,DDR\_BA0,DDR\_BA1,DDR\_BA2, DDR\_A0,DDR\_A1,DDR\_A2,DDR\_A3,DDR\_A4,DDR\_A5,DDR\_A6,DDR\_A7,DDR\_A8,DDR\_A9,DDR\_A10,DDR\_A11,DDR\_A12, DDR\_A13,DDR\_A14,DDR\_A15,DDR\_ODT,DDR\_D0,DDR\_D1,DDR\_D2,DDR\_D3,DDR\_D4,DDR\_D5,DDR\_D6,DDR\_D7, DDR\_D8,DDR\_D9,DDR\_D10,DDR\_D11,DDR\_D12,DDR\_D13,DDR\_D14,DDR\_D15,DDR\_DQM0,DDR\_DQM1,DDR\_DQS0, DDR\_DQSn0,DDR\_DQS1,DDR\_DQSn1 Pins (DDR3, DDR3L - HSTL Mode)

|                                                                                                                                                                                                                                                                           | VDDS                                                                                          | S_DDR = 1.5 V          | Vih              | DDR_VREF +<br>0.1  |     |                    | V  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------|------------------|--------------------|-----|--------------------|----|

| High-level input voltage                                                                                                                                                                                                                                                  | VDDS                                                                                          | 6_DDR = 1.35 V         |                  | DDR_VREF +<br>0.09 |     |                    |    |

|                                                                                                                                                                                                                                                                           | VDDS_DDR = 1.5 V                                                                              |                        | VIL              |                    |     | DDR_VREF –<br>0.1  | V  |

| Low-level input voltage                                                                                                                                                                                                                                                   |                                                                                               | 6_DDR = 1.35 V         |                  |                    |     | DDR_VREF -<br>0.09 |    |

| Hysteresis voltage at an input                                                                                                                                                                                                                                            |                                                                                               |                        | V <sub>HYS</sub> |                    | N/A |                    | V  |

| High level output voltage, driver enabled, pullu pulldown disabled                                                                                                                                                                                                        | High level output voltage, driver enabled, pullup or I <sub>OH</sub> = 8 mA pulldown disabled |                        | Vон              | VDDS_DDR –<br>0.4  |     |                    | V  |

| Low level output voltage, driver enabled, pullu orpulldown disabled                                                                                                                                                                                                       | р                                                                                             | I <sub>OL</sub> = 8 mA | Vol              |                    |     | 0.4                | V  |

| Input leakage current, Receiver disabled, pullu                                                                                                                                                                                                                           | ıp or pul                                                                                     | ldown inhibited        |                  |                    |     | 10                 |    |

| Input leakage current, Receiver disabled, pullup enabled                                                                                                                                                                                                                  |                                                                                               |                        | h                | -240               |     | -80                | μA |

| Input leakage current, Receiver disabled, pulldown enabled                                                                                                                                                                                                                |                                                                                               |                        |                  | 80                 |     | 240                |    |

| Total leakage current, Receiver disabled, pulldown enabled<br>Total leakage current through the terminal connection of a driver-<br>receiver combination that may include a pullup or pulldown. The driver<br>output is disabled and the pullup or pulldown is inhibited. |                                                                                               | loz                    |                  |                    | 10  | μA                 |    |

ECAP0\_IN\_PWM0\_OUT,UART0\_CTSn,UART0\_RTSn,UART0\_RXD,UART0\_TXD,UART1\_CTSn,UART1\_RTSn,UART1\_RXD, UART1\_TXD,I2C0\_SDA,I2C0\_SCL,XDMA\_EVENT\_INTR0,XDMA\_EVENT\_INTR1,WARMRSTn,EXTINTn,TMS,TDO, USB0\_DRVVBUS,USB1\_DRVVBUS (VDDSHV6 = 1.8 V)

| High-level input voltage                                                                                                                                                                                    |                        | Vih              | 0.65 ×<br>VDDSHV6 |      |                   | V  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|-------------------|------|-------------------|----|

| Low-level input voltage                                                                                                                                                                                     |                        | VIL              |                   |      | 0.35 ×<br>VDDSHV6 | V  |

| Hysteresis voltage at an input                                                                                                                                                                              |                        | V <sub>HYS</sub> | 0.18              |      | 0.305             | V  |

| High level output voltage, driver enabled, pullup or pulldown disabled                                                                                                                                      | I <sub>OH</sub> = 4 mA | V <sub>OH</sub>  | VDDSHV6 –<br>0.45 |      |                   | V  |

| Low level output voltage, driver enabled, pullup orpulldown disabled                                                                                                                                        | I <sub>OL</sub> = 4 mA | Vol              |                   |      | 0.45              | V  |

| Input leakage current, Receiver disabled, pullup or pu                                                                                                                                                      | lldown inhibited       |                  |                   |      | 8                 |    |

| Input leakage current, Receiver disabled, pullup enable                                                                                                                                                     | led                    | h                | -161              | -100 | -52               | μA |

| Input leakage current, Receiver disabled, pulldown enabled                                                                                                                                                  |                        |                  | 52                | 100  | 170               |    |

| Total leakage current through the terminal connection of a driver-<br>receiver combination that may include a pullup or pulldown. The driver<br>output is disabled and the pullup or pulldown is inhibited. |                        | loz              |                   |      | 8                 | μA |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/15602</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV A          | PAGE 16                  |

| TABLE I. | Electrical | performance characteristics - Continued. | 1/ | 2/ 3/ |

|----------|------------|------------------------------------------|----|-------|

|          |            |                                          |    |       |

| Test                                                                                                                                                                                                        |                        | Symbol           |                   | Limits |         | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|-------------------|--------|---------|------|

|                                                                                                                                                                                                             |                        |                  | Min               | Тур    | Max     |      |

| DC Electrical Characteristics (Continued) 3                                                                                                                                                                 | <u>}/</u>              |                  |                   |        |         |      |

| ECAP0_IN_PWM0_OUT,UART0_CTSn,UART0_RT<br>UART1_TXD,I2C0_SDA,I2C0_SCL,XDMA_EVENT_<br>USB0_DRVVBUS,USB1_DRVVBUS (VDDSHV6 = 3                                                                                  | INTRO, XDMA EVE        |                  |                   |        | T1_RXD, |      |

| High-level input voltage                                                                                                                                                                                    |                        | Vін              | 2                 |        |         | V    |

| Low-level input voltage                                                                                                                                                                                     |                        | VIL              |                   |        | 0.8     | V    |

| Hysteresis voltage at an input                                                                                                                                                                              |                        | V <sub>HYS</sub> | 0.265             |        | 0.44    | V    |