|     | REVISIONS                                                                 |                 |                   |

|-----|---------------------------------------------------------------------------|-----------------|-------------------|

| LTR | DESCRIPTION                                                               | DATE (YR-MO-DA) | APPROVED          |

| А   | Update boilerplate to current MIL-PRF-38535 requirements PHN              | 17-08-21        | Thomas M. Hess    |

| В   | Update boilerplate paragraphs to current VID description requirements PHN | 23-04-20        | Muhammad A. Akbar |

|     |                                                                           |                 |                   |

|     |                                                                           |                 |                   |

|     |                                                                           |                 |                   |

|     |                                                                           |                 |                   |

|     |                                                                           |                 |                   |

CURRENT DESIGN ACTIVITY CAGE CODE 16236 HAS CHANGED NAMES TO: DLA LAND AND MARITIME COLUMBUS, OHIO 43218-3990

Prepared in accordance with ASME Y14.24

Vendor Item Drawing

| Revision Statu | Revision Status of Sheets |   |   |   |   |   |   |   |   |    |    |    |  |  |  |  |  |

|----------------|---------------------------|---|---|---|---|---|---|---|---|----|----|----|--|--|--|--|--|

| REV            |                           |   |   |   |   |   |   |   |   |    |    |    |  |  |  |  |  |

| SHEET          |                           |   |   |   |   |   |   |   |   |    |    |    |  |  |  |  |  |

| REV            |                           |   |   |   |   |   |   |   |   |    |    |    |  |  |  |  |  |

| SHEET          |                           |   |   |   |   |   |   |   |   |    |    |    |  |  |  |  |  |

| REV            | В                         | В | В | В | В | В | В | В | В | В  | В  | В  |  |  |  |  |  |

| SHEET          | 1                         | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |  |  |  |  |  |

| OHEET         | 1 '     | _    | 0 | 1 -                       | 0              | 0     | <i>'</i> | 0                                         |                                                                             | 10                                                                                                                                    |     | 12   |     |      |      |     |      |            |    |     |      |       |            |

|---------------|---------|------|---|---------------------------|----------------|-------|----------|-------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|------|-----|------|------------|----|-----|------|-------|------------|

| PMIC N/A      |         |      |   | PREPARED BY Phu H. Nguyen |                |       |          |                                           |                                                                             | DLA LAND AND MARITIME COLUMBUS, OHIO 43218-3990 <a href="http://www.landandmaritime.dla.mil">http://www.landandmaritime.dla.mil</a> / |     |      |     |      |      |     |      |            |    |     |      |       |            |

| Original date | e of dr | awin | g | CHECKED BY                |                |       |          |                                           |                                                                             | TITLE                                                                                                                                 |     |      |     |      |      |     |      |            |    |     |      |       |            |

|               |         |      |   |                           | ı              | Phu H | l. Ngu   | ıyen                                      |                                                                             |                                                                                                                                       | MIC | ROC  | IRC | UIT, | DIG  | IT/ | AL ( | CMC        | os | 3.0 | V TO | 5.5 \ | <b>/</b> , |

| YY M          | M DD    |      |   | APPROVED BY               |                |       |          | 12 BIT, 200 KSPS, 4-/8 CHANNEL, LOW POWER |                                                                             |                                                                                                                                       |     |      |     |      |      |     |      |            |    |     |      |       |            |

| 09-1          | 1-09    |      |   |                           | Thomas M. Hess |       |          |                                           | SERIAL ANALOG TO DIGITAL CONVERTER WI<br>AUTOPOWER DOWN, MONOLITHIC SILICON |                                                                                                                                       |     |      |     |      | IH   |     |      |            |    |     |      |       |            |

|               |         |      |   | SIZ                       | Έ              | CA    | GE C     | ODE                                       | :                                                                           |                                                                                                                                       | DW  | 3 NO |     |      |      |     |      |            |    |     |      |       |            |

|               |         |      |   | Α                         | ١              |       | 1        | 623                                       | 6                                                                           |                                                                                                                                       |     |      |     |      | VE   | 32  | /10  | <b>060</b> | 03 | }   |      |       |            |

|               |         |      |   | F                         | REV            | В     |          |                                           |                                                                             |                                                                                                                                       | PAC | ЭE   | 1   | OF   | - 12 | 2   |      |            |    |     |      |       |            |

AMSC N/A 5962-V090-23

### 1. SCOPE

- 1.1 Scope. This drawing documents the general requirements of a high performance 3.0 V to 5.5 V, 12 bit, 200 KSPS, 4-/8 channel, low power serial analog to digital converter with auto power down microcircuit, with an operating temperature range of -55°C to +125°C.

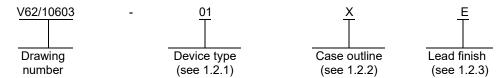

- 1.2 Vendor Item Drawing Administrative Control Number. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

1.2.1 Device type(s).

Device type Generic Circuit function 01 TLV2548-EP 3.0 V to 5.5 V, 12 bit, 200 KSPS, 4-/8 channel, low power serial analog to digital converter with auto power down

1.2.2 Case outline(s). The case outlines are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95 | Package style         |

|----------------|----------------|--------------|-----------------------|

| Х              | 20             | JEDEC MO-153 | Plastic Small outline |

1.2.3 <u>Lead finishes</u>. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator | <u>Material</u>      |

|-------------------|----------------------|

| Α                 | Hot solder dip       |

| В                 | Tin-lead plate       |

| С                 | Gold plate           |

| D                 | Palladium            |

| E                 | Gold flash palladium |

| F                 | Tin-lead alloy       |

| Z                 | Other                |

| DLA LAND AND MARITIME | SIZE<br>A |     | GE CODE<br>16236 | DWG NO.<br>V62/10603 |  |  |

|-----------------------|-----------|-----|------------------|----------------------|--|--|

| COLUMBUS, OHIO        |           | REV | В                | PAGE 2               |  |  |

### 1.3 Absolute maximum ratings. 1/

| Supply voltage range (GND to V <sub>CC</sub> )               | 0.3 V to 6.5 V |

|--------------------------------------------------------------|----------------|

| Analog input voltage range,                                  |                |

| Reference input voltage                                      |                |

| Digital input voltage range                                  |                |

| Operating virtual junction temperature range, T <sub>J</sub> |                |

| Operating free air temperature range, T <sub>A</sub>         | 55°C to 125°C  |

| Storage temperature range (T <sub>STG</sub> )                | 65°C to 150°C  |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds | 260°C          |

| Dissipation ratings:                                         |                |

| Package        | T <sub>A</sub> < 25°C | Derating factor                | T <sub>A</sub> = 125°C |

|----------------|-----------------------|--------------------------------|------------------------|

|                | Power rating          | Above $T_A = 25^{\circ}C \ 2/$ | power rating           |

| Case outline X | 977 mW                | 7.8 mW/°C                      | 195 mW                 |

# 1.4 Recommended operating conditions. 3/

| Paramete                                                                                                       | er                               | Symbol                     | Min | Max   | Unit |

|----------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------|-----|-------|------|

| Supply voltage                                                                                                 |                                  | Vcc                        | 3.0 | 5.5   | V    |

| Analog input voltage 4/                                                                                        |                                  |                            | 0   | Vcc   | V    |

| High level control input voltage                                                                               | V <sub>IH</sub>                  | 2.1                        |     | V     |      |

| Low level control input voltage                                                                                | V <sub>IL</sub>                  |                            | 0.6 | V     |      |

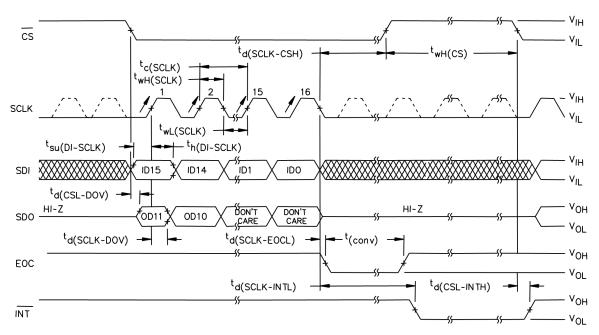

| Delay time, delay from $\overline{\text{CS}}$ fallin edge (See figure 4)                                       | t <sub>d(CSL-FSH)</sub>          | 0.5                        |     | SCLKs |      |

| Delay time, delay from 16 <sup>th</sup> SC rising edge (FS = 1), or 17 <sup>th</sup> risi (See figure 4 and 7) | t <sub>d</sub> (SCLK-CSH)        | 0.5                        |     | SCLKs |      |

| Setup time, FS rising edge before (See figure 4)                                                               | ore SCLK falling edge            | t <sub>su(FSH-SCLKL)</sub> | 20  |       | ns   |

| Hold time, FS hold high after S (See figure 4)                                                                 | CLK falling edge                 | t <sub>h(FSH-SCLKL)</sub>  | 30  |       | ns   |

| Pulse width, $\overline{\text{CS}}$ high time (See                                                             | figure 4 and 7)                  | t <sub>wH(CS)</sub>        | 100 |       | ns   |

| Pulse width, FS high time (See                                                                                 | t <sub>wH(FS)</sub>              | 0.75                       |     | SCLKs |      |

| SCLK cycle time                                                                                                | $V_{CC}$ = 3.0 V to 3.6 V        | $t_{c(SCLK)}$              | 67  | 10000 | ns   |

| (See figure 4 and 7)                                                                                           | V <sub>CC</sub> = 4.5 V to 5.5 V |                            | 50  | 10000 | ns   |

- Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- This is the inverse of the traditional junction to ambient thermal resistance (R<sub>θJA</sub>). Thermal resistance is not production tested and the value given are for informational purposes only.

- 3/ Use of this product beyond the manufacturers design rules or stated parameters is done at the user's risk. The manufacturer and/or distributor maintain no responsibility or liability for product used beyond the stated limits.

- When binary output format is used, analog input voltages greater than that applied to REFP convert as all ones (111111111111), while input voltages less than that applied to REFM convert as all zeros (00000000000). The device is functional with reference down to 1 V. (VREFP VREFM 1); however, the electrical specifications are no longer applicable.

| DLA LAND AND MARITIME | SIZE<br>A |     | GE CODE<br>16236 | DWG NO.<br>V62/10603 |  |  |

|-----------------------|-----------|-----|------------------|----------------------|--|--|

| COLUMBUS, OHIO        |           | REV | В                | PAGE 3               |  |  |

| Para                                                                                                               | meter                   |                         | Symbol                                               | Min                          | Max                     | Unit |

|--------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|------------------------------------------------------|------------------------------|-------------------------|------|

| Pulse width, SCLK low time                                                                                         | V <sub>CC</sub> = 4.5 V |                         | t <sub>wL(SCLK)</sub>                                | 22                           |                         | ns   |

| (See figure 4 and 7)                                                                                               | V <sub>CC</sub> = 3.0 V |                         |                                                      | 27                           |                         |      |

| Pulse width, SCLK high time                                                                                        | V <sub>CC</sub> = 4.5 V |                         | t <sub>wH(SCLK)</sub>                                | 22                           |                         |      |

| (See figure 4 and 7)                                                                                               | V <sub>CC</sub> = 3.0 V |                         |                                                      | 27                           |                         |      |

| Setup time, SDI valid before factive) or the rising edge of S                                                      |                         |                         | t <sub>su(DI-SCLK)</sub>                             | 25                           |                         |      |

| Hold time, SDI hold valid after active) or the rising edge of S                                                    |                         |                         | $t_{\text{h(DI-SCLK)}}$                              | 5                            |                         |      |

| Delay time, delay from $\overline{CS}$ falli (See figure 4 and 7)                                                  | ng edge to SD           | O valid                 | $t_{\text{d(CSL-DOV)}}$                              |                              | 25                      |      |

| Delay time, delay from FS fall (See figure 4)                                                                      | ing edge to SD          | t <sub>d(FSL-DOV)</sub> |                                                      | 25                           |                         |      |

| Delay time, delay from<br>SCLK falling edge (FS is<br>active) or SCLK rising edge                                  | V <sub>CC</sub> = 5.5 V | SDO = 0 pF              |                                                      | 0.5 SCLK                     | + 5 TYP                 |      |

| (FS = 1) to SDO valid<br>(See figure 4 and 7)                                                                      |                         | SDO = 60 pF             | t <sub>d(SCLK-DOV)</sub>                             |                              | 0.5 SCLK + 24           |      |

| For a date code later than xxx, see the data code from                                                             | $V_{CC}$ = 3.0 $V$      | SDO = 0 pF              |                                                      | 0.5 SCLK                     | + 12 TYP                |      |

| manufacturer data.                                                                                                 |                         | SDO = 60 pF             |                                                      |                              | 0.5 SCLK + 33           |      |

| Delay time, delay from 17 <sup>th</sup> S0 active), or the 16 <sup>th</sup> falling edge edge (See figure 4 and 7) |                         |                         | t <sub>d</sub> (SCLK-EOCL)                           | 45                           |                         |      |

| Delay time, delay from 16 <sup>th</sup> S0 edge (FS = 1), or from the 17 rising edge. (See figure 4, 5, 6          | th rising edge S        |                         | t <sub>d</sub> (SCLK-INTL)                           | Min t <sub>(conv)</sub>      |                         |      |

| Delay time, delay from $\overline{\text{CS}}$ falli $\overline{\text{INT}}$ rising edge (See figure 4,             | ng edge or FS           | rising edge to          | $t_{d(CLK\text{-INTH})}$ or $t_{d(FSH\text{-INTH})}$ |                              | 50                      |      |

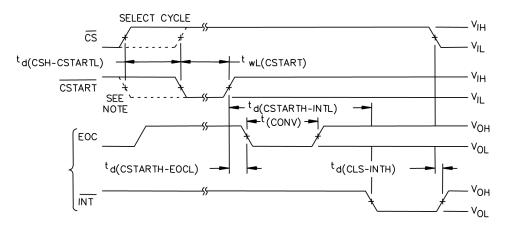

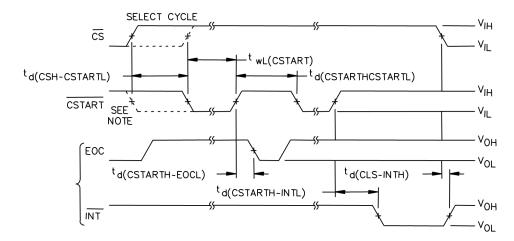

| Delay time, delay from $\overline{\text{CS}}$ risinedge (See figure 5 and 6)                                       |                         |                         | t <sub>d(CSH-</sub><br>CSTARTL)                      | 100                          |                         |      |

| Delay time, delay from CSTAR edge (See figure 5 and 6)                                                             | T rising edge to        | o EOC falling           | t <sub>d(CSTARTH-</sub><br>EOCL)                     |                              | 50                      | ns   |

| Pulse width, CSTART low time                                                                                       | (See figure 5           | and 6)                  | t <sub>wL(CSTART)</sub>                              | Min<br>t <sub>(sample)</sub> |                         | μs   |

| Delay time, delay from CSTAR falling edge (See figure 6)                                                           | T rising edge to        | o CSTART                | t <sub>d(CSTARTH-</sub><br>CSTARTL)                  | Min t <sub>(conv)</sub>      |                         | μs   |

| Delay time, delay from CSTART rising edge to INT falling edge (See figure 6 and 7)                                 |                         |                         | t <sub>d(CSTARTH-</sub> INTL)                        | Max                          | t <sub>(conv)</sub> TYP | μs   |

| Operation free air temperature                                                                                     | •                       |                         | TA                                                   | -55                          | 125                     | °C   |

| DLA LAND AND MARITIME | SIZE<br>A |     | SE CODE<br>16236 | DWG NO.<br>V62/10603 |  |

|-----------------------|-----------|-----|------------------|----------------------|--|

| COLUMBUS, OHIO        |           | REV | В                | PAGE 4               |  |

#### 2. APPLICABLE DOCUMENTS

### JEDEC - SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JEDEC PUB 95 - Registered and Standard Outlines for Semiconductor Devices

(Copies of these documents are available online at http://www.jedec.org)

# 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 Design, construction, and physical dimension. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

- 3.5.1 Case outline. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

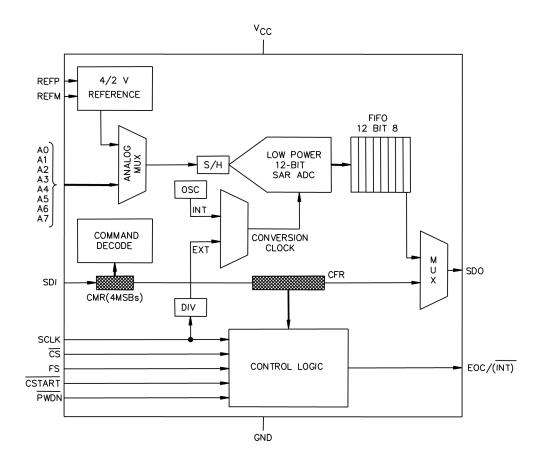

- 3.5.3 Functional block diagram. The functional block diagram shall be as shown in figure 3.

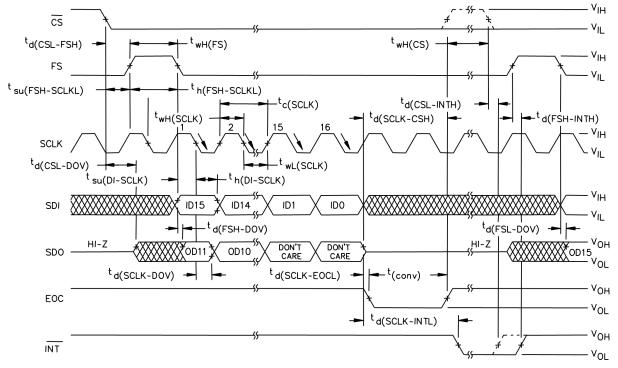

- 3.5.4 <u>Timing waveforms</u>. The timing waveforms shall be as shown in figure 4 7.

| DLA LAND AND MARITIME | SIZE<br>A |     | GE CODE<br>16236 | DWG NO.<br>V62/10603 |

|-----------------------|-----------|-----|------------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В                | PAGE 5               |

TABLE I. Electrical performance characteristics.  $\underline{1}/$

| Test                                                                           | Symbol              | Conditions                                                                                                                        |                   |                               | Lim   | nits       | Unit |

|--------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------|-------|------------|------|

|                                                                                |                     | <u>2</u> /                                                                                                                        |                   |                               | Min   | Max        |      |

| High level output voltage                                                      | Vон                 | $V_{CC} = 5.5 \text{ V}, I_{OH} = -6$                                                                                             | 0.2 m/            | A at 30 pF load               | 2.4   |            | V    |

|                                                                                |                     | V <sub>CC</sub> = 3.0 V, I <sub>OH</sub> = -20 µA at 30 pF load                                                                   |                   | Vcc - 0.2                     |       |            |      |

| Low level output voltage                                                       | Vol                 | V <sub>CC</sub> = 5.5 V, I <sub>OL</sub> = 0.8 mA at 30 pF load<br>V <sub>CC</sub> = 3.0 V, I <sub>OL</sub> = 20 μA at 30 pF load |                   |                               | 0.4   |            |      |

|                                                                                |                     |                                                                                                                                   |                   |                               | 0.1   |            |      |

| Off state output current                                                       | loz                 | $V_O = V_{CC}$                                                                                                                    | CS                | = V <sub>CC</sub>             |       | 2.5        | μA   |

| (high-impedance state)                                                         |                     | V <sub>O</sub> = 0                                                                                                                | CS                | = V <sub>CC</sub>             | -2.5  |            |      |

| High level input current                                                       | lih                 | $V_I = V_{CC}$                                                                                                                    |                   |                               |       | 2.5        |      |

| Low level input current                                                        | lıL                 | V <sub>I</sub> = 0 V                                                                                                              |                   |                               |       | 2.5        |      |

|                                                                                |                     | CS at 0 V, Ext ref                                                                                                                | Vc                | <sub>C</sub> = 4.5 V to 5.5 V |       | 2          | mA   |

| Operating supply current, normal                                               |                     |                                                                                                                                   | Vc                | c = 3.0 V to 3.3 V            |       | 1          |      |

| short sampling                                                                 | Icc                 | CS at 0 V, Int ref                                                                                                                |                   | c = 4.5 V to 5.5 V            |       | 2.4        |      |

|                                                                                |                     | ·                                                                                                                                 | Vc                | c = 3.0 V to 3.3 V            |       | 1.7        |      |

|                                                                                |                     | CS at 0 V, Ext ref                                                                                                                |                   | c = 4.5 V to 5.5 V            | 1.1   | TYP        |      |

| Operating supply current, extended                                             |                     |                                                                                                                                   |                   | c = 3.0 V to 3.3 V            | 1     | TYP        |      |

| sampling                                                                       |                     | CS at 0 V, Int ref                                                                                                                | _                 | c = 4.5 V to 5.5 V            | 2.1   | TYP        |      |

|                                                                                |                     | ,                                                                                                                                 |                   | <sub>C</sub> = 3.0 V to 3.3 V | 1.6   | TYP        |      |

| Power down supply current for all digital input,                               | I <sub>CC(PD)</sub> | V <sub>CC</sub> = 4.5 V to 5.5 V, Ext clock                                                                                       |                   | 1                             | TYP   | μA         |      |

| $0 \le V_1 \le 0.3 \text{ V or}$<br>$V_1 \ge V_{CC} - 0.3 \text{ V, SCLK} = 0$ |                     | V <sub>CC</sub> = 3.0 V to 3.3 V, Ext clock                                                                                       |                   |                               | 1     | TYP        |      |

| Auto power down current for all digital input,                                 | Icc(autopwdn)       | V <sub>CC</sub> = 4.5 V to 5.5 V, Ext clock, Ext ref                                                                              |                   | 1.0<br><u>3</u> /             | TYP   |            |      |

| $0 \le V_1 \le 0.3 \text{ V or}$<br>$V_1 \ge V_{CC} - 0.3 \text{ V, SCLK} = 0$ | , ,                 | V <sub>CC</sub> = 3.0 V to 3.3 V, Ext clock, Ext ref                                                                              |                   | 1.0                           | TYP   |            |      |

| Selected channel leakage current                                               |                     | Selected channel a                                                                                                                | t V <sub>CC</sub> |                               | _     | 2.5        |      |

| •                                                                              |                     | Selected channel a                                                                                                                | t 0 V             |                               |       | 2.5        |      |

| Maximum static analog reference current into REFP (use external reference)     |                     | VREFP = V <sub>CC</sub> = 5.5 V, VREFM = GND                                                                                      |                   | 1                             | TYP   |            |      |

| Input capacitance                                                              | Ci                  | Analog inputs                                                                                                                     |                   |                               |       | 50         | рF   |

|                                                                                |                     | Control inputs                                                                                                                    |                   |                               |       | 25         |      |

| Input MUX ON resistance                                                        | Zi                  | V <sub>CC</sub> = 4.5 V                                                                                                           |                   |                               |       | 500        | Ω    |

|                                                                                |                     | V <sub>CC</sub> = 2.7 V                                                                                                           |                   |                               | 600   |            |      |

| AC specifications                                                              |                     |                                                                                                                                   |                   |                               |       |            |      |

| Signal to noise ratio + distortion                                             | SINAD               | f <sub>I</sub> = 12 kHz at 200 KS                                                                                                 | SPS               |                               | 65    |            | dB   |

| Total harmonic distortion                                                      | THD                 | f <sub>I</sub> = 12 kHz at 200 KSPS                                                                                               |                   |                               | -73   |            |      |

|                                                                                |                     |                                                                                                                                   |                   | All other temperature         |       | -75        |      |

| Effective number of bits                                                       | ENOB                | f <sub>i</sub> = 12 kHz at 200 KSPS                                                                                               |                   | 11.6                          | TYP   | Bits       |      |

| Spurious free dynamic range                                                    | SFDR                | f <sub>I</sub> = 12 kHz at 200 KS                                                                                                 | SPS               |                               |       | -75        | dB   |

| Analog input                                                                   |                     |                                                                                                                                   |                   |                               |       |            |      |

| Full power bandwidth, -3 dB                                                    |                     |                                                                                                                                   |                   |                               | 1 TY  | Р          | MHz  |

| Full power bandwidth, -1 dB                                                    |                     |                                                                                                                                   |                   |                               | 500 T | <u> YP</u> | kHz  |

See footnotes at end of table.

| DLA LAND AND MARITIME | SIZE<br>A |     | E CODE<br>6236 | DWG NO.<br>V62/10603 |

|-----------------------|-----------|-----|----------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В              | PAGE 6               |

TABLE I. Electrical performance characteristics - Continued. 1/

| Tes                               | st                        | Symbol                |                                                   | Conditions                                      | Limi       | ts              | Unit    |

|-----------------------------------|---------------------------|-----------------------|---------------------------------------------------|-------------------------------------------------|------------|-----------------|---------|

|                                   |                           |                       |                                                   | <u>2</u> /                                      | Min        | Max             |         |

| Reference specifica               | ations <u>5</u> / (0.1 µF | and 10 μF betwee      | n REFP and RE                                     | FM pins)                                        |            |                 |         |

| Positive reference i              |                           | REFP                  | V <sub>CC</sub> = 3.0 V to                        |                                                 | 2          | Vcc             | V       |

| Negative reference                | input voltage             | REFM                  | $V_{CC}$ = 3.0 V to                               | 3.3 V                                           | 0          | 2               |         |

|                                   |                           |                       | V <sub>CC</sub> = 5.5 V                           | $\overline{\text{CS}}$ = 1, SCLK = 0, (off)     | 100        |                 | МΩ      |

| Reference input imp               | pedance                   |                       |                                                   | $\overline{\text{CS}}$ = 0, SCLK = 20 MHz, (on) | 20         |                 | kΩ      |

|                                   |                           |                       | V <sub>CC</sub> = 3 V                             | $\overline{\text{CS}}$ = 1, SCLK = 0, (off)     | 100        |                 | МΩ      |

|                                   |                           |                       |                                                   | $\overline{CS}$ = 0, SCLK = 15 MHz, (on)        | 20         |                 | kΩ      |

| Reference input vol               | Itage difference          | REFP - REFM           | V <sub>CC</sub> = 3.0 V to                        | 5.5 V                                           | 2          | V <sub>CC</sub> | V       |

|                                   |                           |                       | V <sub>CC</sub> = 5.5 V                           | VREF SELECT = 4 V                               | 3.85       | 4.15            | V       |

| Internal reference v              | oltage                    | REFP - REFM           | V <sub>CC</sub> = 5.5 V                           | VREF SELECT = 2 V                               | 1.925      | 2.075           |         |

|                                   |                           |                       | V <sub>CC</sub> = 3.0 V                           | VREF SELECT = 2 V                               | 1.925      | 2.075           |         |

| Internal reference s              | start up time             |                       | $V_{CC}$ = 5.5 V, 3 V with 10 µF compensation cap |                                                 | 20         | TYP             | ms      |

| Internal reference to coefficient | emperature                |                       |                                                   |                                                 | 2.075      | 40<br>5/        | PPM/ °C |

| Operating characte                | eristics                  |                       |                                                   |                                                 |            |                 |         |

| Integral linearity err            | or (INL) <u>6</u> /       | EL                    |                                                   |                                                 |            | ±1.2            | LSB     |

| Differential linearity            | error (DNL)               | ED                    | <u>7</u> /                                        |                                                 |            | ±1.2            |         |

| Offset error 8/                   |                           | EO                    | <u>7</u> /                                        | T <sub>A</sub> = 25°C and 125°C                 | -4         | 6               |         |

|                                   |                           |                       |                                                   | T <sub>A</sub> = -55°C                          | -4         | 6.2             |         |

| Full scale error 8/               |                           | EFS                   | <u>7</u> /                                        | T <sub>A</sub> = 25°C and 125°C                 | -4         | 6               |         |

|                                   |                           |                       |                                                   | T <sub>A</sub> = -55°C                          | -4         | 7.6             |         |

|                                   |                           |                       | SDI = B000h                                       |                                                 | 800 h      | (2048D)         |         |

| Self test output cod              | le <u>9</u> /             |                       | SDI = C000h                                       |                                                 | 000h       | (0D)            |         |

|                                   |                           |                       | SDI = D000h                                       |                                                 | FFFh       | (4095D)         |         |

| Conversion time                   | Internal OSC              | t <sub>(conv)</sub>   |                                                   |                                                 |            | 4.65            | μs      |

|                                   | External SCLK             |                       |                                                   |                                                 | (14 x DIV) | / fsclk         |         |

| Sampling time                     |                           | t <sub>(sample)</sub> | With a maximu<br>of 1 kW input<br>source impeda   |                                                 | 600        |                 | ns      |

- 1/ Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

- Over operating free air temperature range,  $V_{CC} = V_{REFP} = 3 \text{ V}$  to 5.5 V,  $V_{REFM} = 0 \text{ V}$ , SCLK frequency = 20 MHz at 5 V, 15 MHz at 3 V (unless otherwise noted). All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$

- 3/ 1.2 mA if internal reference is used, 165  $\mu$ A if internal clock is used.

- 4/ 0.8 mA if internal reference is used, 116 µA if internal clock is used.

- 5/ Specified by design.

- 6/ Linear error is the maximum deviation from the best straight line through the A/D transfer characteristics.

- Analog input voltages greater than that applied to REFP convert as all ones (111111111111), while input voltages less than that applied to REFM convert as all zeros (000000000000).

- 8/ Zero error is the difference between 000000000000 and the converted output for zero input voltage: full scale error is the difference between 11111111111 and the converted output for full scale input voltage.

- 9/ Both the input data and the output codes are expressed in positive logic.

| DLA LAND AND MARITIME | SIZE<br>A | _   | SE CODE<br>16236 | DWG NO.<br>V62/10603 |

|-----------------------|-----------|-----|------------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В                | PAGE 7               |

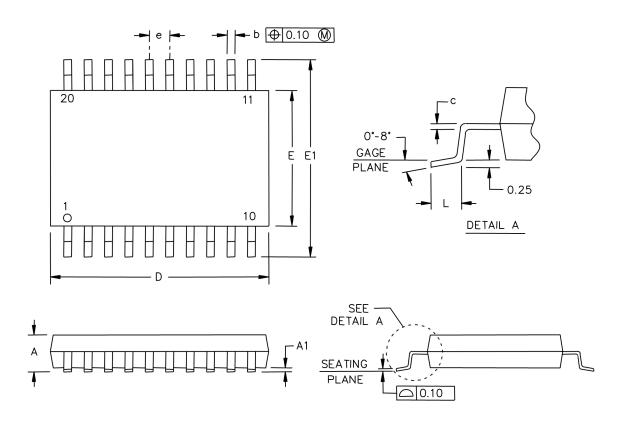

Dimensions

| Symbol | Millim | eters | Symbol | Millim | eters |

|--------|--------|-------|--------|--------|-------|

| •      | Min    | Max   | •      | Min    | Max   |

| Α      |        | 1.20  | Е      | 4.30   | 4.50  |

| A1     | 0.05   | 0.15  | E1     | 6.20   | 6.60  |

| b      | 0.19   | 0.30  | е      | 0.65   | BSC   |

| С      | 0.15   | NOM   | L      | 0.50   | 0.75  |

| D      | 6.40   | 6.60  |        |        | •     |

# NOTES:

- 1. All linear dimensions are in millimeters..

- This drawing is subject to change without notice.

Body dimensions do not include mold flash or protrusion not to exceed 0.15.

- Falls within JEDEC MO-153.

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE<br>A |     | GE CODE<br>16236 | DWG NO.<br>V62/10603 |

|-----------------------|-----------|-----|------------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В                | PAGE 8               |

Case outlines X

| Terminal number | Terminal symbol | Terminal number | Terminal symbol |

|-----------------|-----------------|-----------------|-----------------|

| 1               | SDO             | 11              | A5              |

| 2               | SDI             | 12              | A6              |

| 3               | SCLK            | 13              | A7              |

| 4               | EOC(INT)        | 14              | CSTART          |

| 5               | Vcc             | 15              | GND             |

| 6               | A0              | 16              | <u>PWDN</u>     |

| 7               | A1              | 17              | FS              |

| 8               | A2              | 18              | REFM            |

| 9               | A3              | 19              | REFP            |

| 10              | A4              | 20              | CS              |

FIGURE 2. Terminal connections.

FIGURE 3. Functional block diagram.

| DLA LAND AND MARITIME | SIZE<br>A |     | GE CODE<br>16236 | DWG NO.<br>V62/10603 |

|-----------------------|-----------|-----|------------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В                | PAGE 9               |

CRITICAL TIMING, DSP MODE(NORMAL SAMPLING, FS IS ACTIVE)

FIGURE 4. Timing waveforms.

CRITICAL TIMING (EXTENDED SAMPLING, SINGLE SHOT)

FIGURE 5. Timing waveforms.

| DLA LAND AND MARITIME | SIZE<br>A | _   | SE CODE<br>16236 | DWG NO.<br>V62/10603 |

|-----------------------|-----------|-----|------------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В                | PAGE 10              |

CRITICAL TIMING (EXTENDED SAMPLING, REPEAT/SWEEP/REPEAT SWEEP)

# NOTES:

1. CSTART falling edge may come before the riding edge of  $\overline{CS}$  but no sooner than the fifth SCLK of the SELECT CYCLE. In this case, the actual sampling time is measured from the rising edge  $\overline{CS}$  to the rising edge of  $\overline{CSTART}$ .

FIGURE 6. Timing waveforms.

CRITICAL TIMING, MICROPROCESSOR MODE(NORMAL SAMPLING, FS=1)

FIGURE 7. Timing waveforms.

| DLA LAND AND MARITIME | SIZE<br>A |     | GE CODE<br>16236 | DWG NO.<br>V62/10603 |

|-----------------------|-----------|-----|------------------|----------------------|

| COLUMBUS, OHIO        |           | REV | В                | PAGE 11              |

#### 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

### 5. PREPARATION FOR DELIVERY

5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

# 6. NOTES

- 6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

- 6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

- 6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item. DLA Land and Maritime maintains an online database of all current sources of supply at <a href="https://landandmaritimeapps.dla.mil/programs/smcr/default.aspx">https://landandmaritimeapps.dla.mil/programs/smcr/default.aspx</a>

| Vendor item drawing administrative control number 1/ | Device<br>manufacturer<br>CAGE code | Vendor part number |

|------------------------------------------------------|-------------------------------------|--------------------|

| V62/10603-01XE                                       | 01295                               | TLV2548MPWREP      |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

CAGE code Source of supply

01295 Texas Instruments, Inc.

Semiconductor Group

8505 Forest Lane

P.O. Box 660199 Dallas, TX 75243

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE<br>A | CAGE CODE<br>16236 |   | DWG NO.<br>V62/10603 |

|-----------------------------------------|-----------|--------------------|---|----------------------|

|                                         |           | REV                | В | PAGE 12              |