|     | REVISIONS                                                                                                 |                 |                   |

|-----|-----------------------------------------------------------------------------------------------------------|-----------------|-------------------|

| LTR | DESCRIPTION                                                                                               | DATE (YR-MO-DA) | APPROVED          |

| Α   | Figure 1, case outline X, corrected the "e" dimension. Updated drawing to remove class M requirements drw | 12-07-25        | Charles F. Saffle |

| В   | Redrawn. Update paragraphs to MIL-PRF-38535 requirements drw                                              | 18-08-24        | Charles F. Saffle |

| С   | Figure 2, case outline X, made corrections to terminal numbers 10, 60, and 61rrp                          | 19-05-20        | Charles F. Saffle |

| REV                            |        |        |     |                                   |            |                 |         |    |                                                            |                                                                                                                 |    |   |   |   |      |    |    |    |    |    |

|--------------------------------|--------|--------|-----|-----------------------------------|------------|-----------------|---------|----|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----|---|---|---|------|----|----|----|----|----|

| SHEET                          |        |        |     |                                   |            |                 |         |    |                                                            |                                                                                                                 |    |   |   |   |      |    |    |    |    |    |

| REV                            | С      | С      | С   | С                                 | С          | С               | С       | С  | С                                                          | С                                                                                                               |    |   |   |   |      |    |    |    |    |    |

| SHEET                          | 15     | 16     | 17  | 18                                | 19         | 20              | 21      | 22 | 23                                                         | 24                                                                                                              |    |   |   |   |      |    |    |    |    |    |

| REV STATUS                     |        |        |     | REV                               | ′          |                 | С       | С  | С                                                          | С                                                                                                               | С  | С | С | С | С    | С  | С  | С  | С  | С  |

| OF SHEETS                      |        |        |     | SHE                               | ET         |                 | 1       | 2  | 3                                                          | 4                                                                                                               | 5  | 6 | 7 | 8 | 9    | 10 | 11 | 12 | 13 | 14 |

| PMIC N/A                       |        |        |     | PRE                               | PARED      |                 | /onnell |    |                                                            | DLA LAND AND MARITIME                                                                                           |    |   |   |   |      |    |    |    |    |    |

| STAN<br>MICRO<br>DRA           | CIRC   | CUIT   |     | CHE                               | CKED       |                 | thadia  |    |                                                            | COLUMBUS, OHIO 43218-3990 <a href="https://www.dla.mil/LandandMaritime">https://www.dla.mil/LandandMaritime</a> |    |   |   |   |      |    |    |    |    |    |

| THIS DRAWIN<br>FOR US          | SE BY  | ALL    | BLE | APPI                              | ROVEI<br>C | D BY<br>Charles | F. Saff | le |                                                            | MICROCIRCUIT, DIGITAL-LINEAR, 12 BIT,                                                                           |    |   |   |   | •    |    |    |    |    |    |

| DEPAR<br>AND AGEN<br>DEPARTMEN | CIES   | OF THE | _   | DRAWING APPROVAL DATE<br>11-07-01 |            |                 |         |    | 1 GSPS, ANALOG TO DIGITAL CONVERTER,<br>MONOLITHIC SILICON |                                                                                                                 |    |   |   |   |      |    |    |    |    |    |

| AMS                            | SC N/A |        |     | REV                               | ISION      |                 | 2       |    |                                                            | SIZE CAGE CODE<br>A <b>67268 5962-0</b>                                                                         |    |   |   |   | 0924 | 0  |    |    |    |    |

|                                |        |        |     |                                   |            | ;               | SHEET   | -  | 1                                                          | OF 2                                                                                                            | 24 |   |   |   |      |    |    |    |    |    |

### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device class Q) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels is reflected in the PIN.

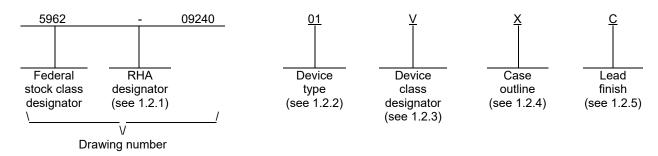

- 1.2 PIN. The PIN is as shown in the following example:

- 1.2.1 RHA designator. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type</u>. The device type identifies the circuit function as follows:

| Device type | Generic number | Circuit function                            |

|-------------|----------------|---------------------------------------------|

| 01          | ADS5400-SP     | 12 bit, 1 GSPS, analog to digital converter |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

<u>Device class</u> <u>Device requirements documentation</u>

Q or V Certification and qualification to MIL-PRF-38535

1.2.4 Case outline. The case outline is as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style                         |

|----------------|------------------------|------------------|---------------------------------------|

| X              | See figure 1           | 100              | Ceramic nonconductive tie-bar package |

5962-09240

2

SHEET

1.2.5 Lead finish. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     |

|----------------------------------------------------|------------------|---------------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>C |

## 1.3 Absolute maximum ratings. 1/, 2/

| Supply voltage: 5 V analog supply voltage (AVDD5) to ground (GND) 3 V analog supply voltage (AVDD3) to GND 3 V digital supply voltage (DVDD3) to GND AINP, AINN to GND (voltage difference between pin and ground) AINP to AINN (voltage difference between pins, common mode at AVDD5/2): 3/ | 5 V<br>5 V<br>0.5 V to 4.5 V <u>3</u> /                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Short duration  Continuous AC signal  Continuous DC signal  CLKINP, CLKINN to GND (voltage difference between pin and ground)                                                                                                                                                                 | 1.25 V to 3.75 V<br>1.75 V to 3.25 V                                  |

| CLKINP to CLKINN (voltage difference between pins, common mode at AVDD5/2): 3/ Continuous AC signal                                                                                                                                                                                           | 2 V to 3 V                                                            |

| RESETP to RESETN (voltage difference between pins): 3/ Continuous AC signal                                                                                                                                                                                                                   | 2 V to 3 V                                                            |

| SDENB, SDIO, SCLK to GND (voltage difference between pin and ground)  ENA1BUS, ENPWD, ENEXTREF to GND (voltage difference between pin and ground)  Maximum junction temperature (TJ)                                                                                                          | -0.3 V to (AVDD3 + 0.3 V) 3/<br>-0.3 V to (AVDD5 + 0.3 V) 3/<br>150°C |

| Storage temperature range                                                                                                                                                                                                                                                                     | 2 kV                                                                  |

| Thermal resistance, junction-to-ambient (θJA)                                                                                                                                                                                                                                                 |                                                                       |

| Supply voltage: AVDD5 to GND AVDD3 to GND DVDD3 to GND Analog input:                                                                                                                                                                                                                          | 3.135 V to 3.465 V                                                    |

| Full scale differential input range                                                                                                                                                                                                                                                           |                                                                       |

| Differential output load Clock (CLK) input: CLK input sample rate (sine wave) Clock amplitude, differential Clock duty cycle                                                                                                                                                                  | 100 MSPS to 1000 MSPS<br>0.6 VPP to 1.5 VPP<br>45% to 55%             |

| Case operating temperature range (TC)                                                                                                                                                                                                                                                         | -55°C to +125°C                                                       |

<sup>1/</sup> Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

3/ Valid when supplies are within recommended operating range.

| STANDARD MICROCIRCUIT DRAWING DLA LAND AND MARITIME COLUMBUS, OHIO 43218-3990 | SIZE<br><b>A</b> |                     | 5962-09240 |

|-------------------------------------------------------------------------------|------------------|---------------------|------------|

|                                                                               |                  | REVISION LEVEL<br>C | SHEET 3    |

1

This package has built in vias that electrically and thermally connect the bottom of the die to a pad on the bottom of the package. To efficiently remove heat and provide a low impedance ground path, a thermal land is required on the surface of the printed circuit board (PCB) directly underneath the body of the package. During normal surface mount flow solder operations, the heat pad on the underside of the package is soldered to this thermal land creating an efficient thermal path. Normally, PCB thermal land has a number of thermal vias within it that provide a thermal path to internal copper areas (or to the opposite side of the PCB) that provide for more efficient heat removal. The manufacturer recommends an 11.9 mm<sup>2</sup> board mount thermal pad. This allows maximum area for thermal dissipation, while keeping leads away from the pad area to prevent solder bridging. A sufficient quantity of thermal/electrical vias must be included to keep the device within recommended operating conditions. This pad must be electrically at ground potential.

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

#### DEPARTMENT OF DEFENSE STANDARDS

MIL-STD-883 - Test Method Standard Microcircuits.

MIL-STD-1835 - Interface Standard Electronic Component Case Outlines.

#### DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 - List of Standard Microcircuit Drawings.

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at https://quicksearch.dla.mil).

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 as specified herein, or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V.

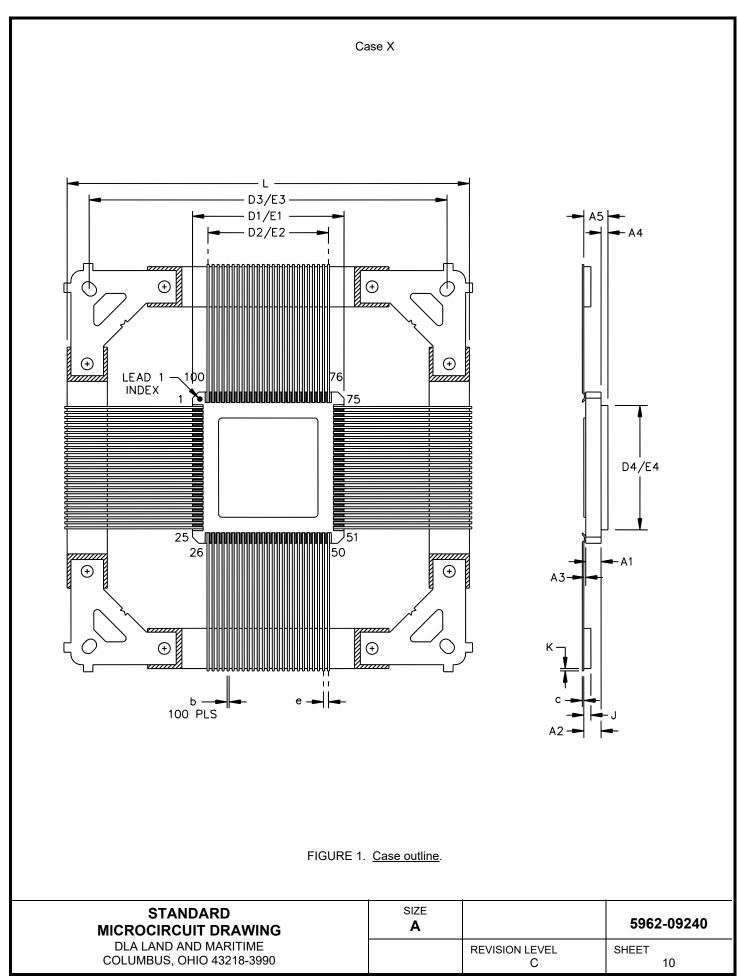

- 3.2.1 <u>Case outline</u>. The case outline shall be in accordance with 1.2.4 herein and figure 1.

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

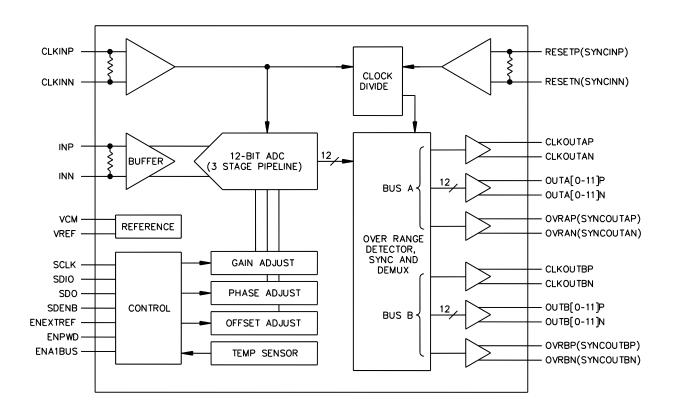

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 3.

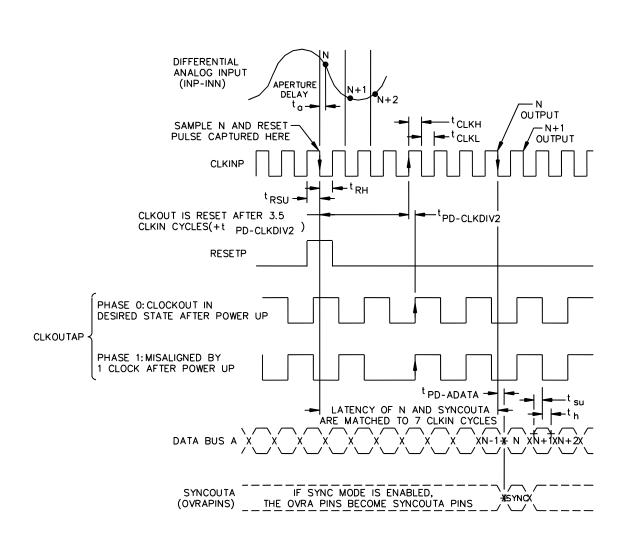

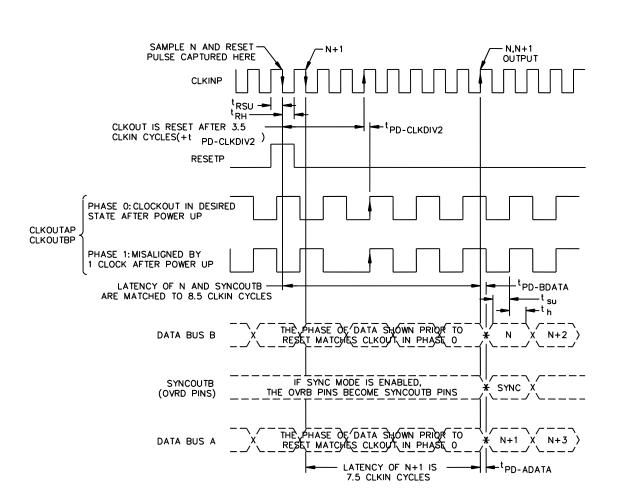

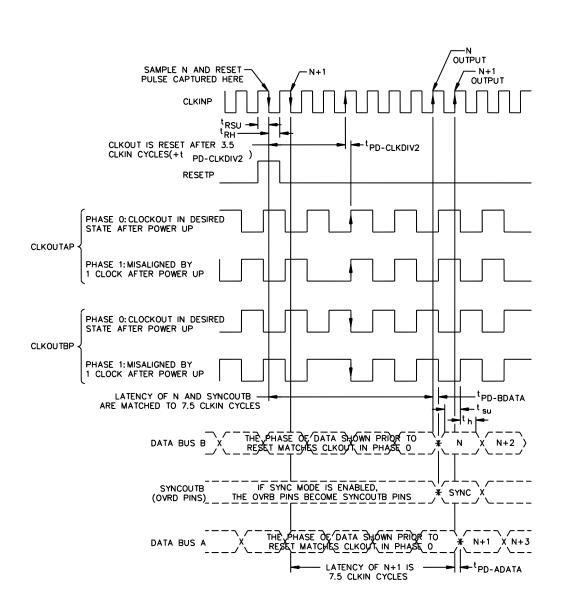

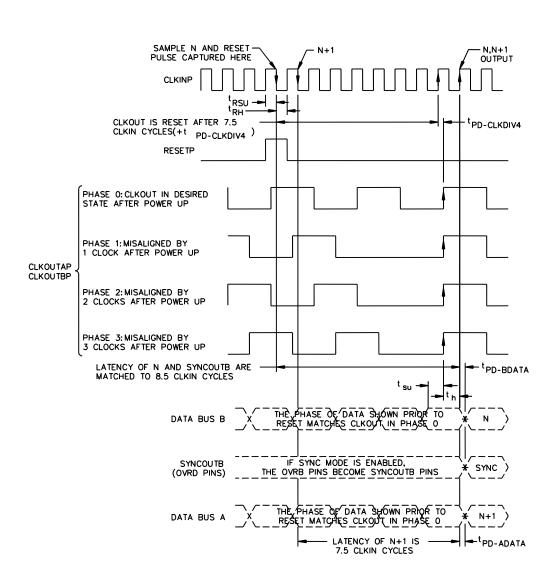

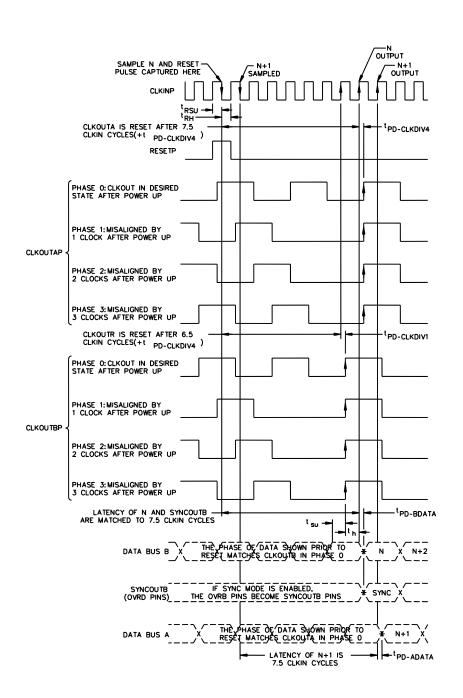

- 3.2.4 Timing waveforms. The timing waveforms shall be as specified on figure 4.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table I.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-09240 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>C | SHEET 4    |

# TABLE I. <u>Electrical performance characteristics</u>.

| Test                                              | Symbol | Conditions <u>1</u> /<br>-55°C ≤ T <sub>C</sub> ≤ +125°C | Group A subgroups | Device<br>type | Lin  | nits | Unit |

|---------------------------------------------------|--------|----------------------------------------------------------|-------------------|----------------|------|------|------|

|                                                   |        | unless otherwise specified                               |                   |                | Min  | Max  |      |

| Analog inputs section                             |        |                                                          |                   |                |      |      |      |

| Full scale differential input range               |        | Programmable                                             | 1, 2, 3           | 01             | 1.52 | 2    | VPP  |

| Reference voltage                                 | VREF   |                                                          | 1, 2, 3           | 01             | 1.98 | 2.02 | V    |

| Dynamic accuracy section                          |        |                                                          |                   |                |      |      |      |

| Resolution                                        |        | No missing codes                                         | 4, 5, 6           | 01             | 12   |      | Bits |

| Differential linearity error                      | DNL    | fin = 125 MHz                                            | 4, 5, 6           | 01             | -1   | 2.5  | LSB  |

| Integral non- linearity error                     | INL    | fin = 125 MHz                                            | 4, 5, 6           | 01             | -4.5 | 4.5  | LSB  |

| Offset error voltage                              |        | Default is trimmed near 0 mV                             | 1, 2, 3           | 01             | -2.5 | 2.5  | mV   |

| Power supply section 2/                           |        |                                                          |                   |                |      |      |      |

| 5 V analog supply current<br>(Bus A and B active) | IAVDD5 | fin = 125 MHz, fs = 1 GSPS                               | 1, 2, 3           | 01             |      | 245  | mA   |

| 5 V analog supply current<br>(Bus A active)       | IAVDD5 | fin = 125 MHz, fs = 1 GSPS                               | 1, 2, 3           | 01             |      | 255  | mA   |

| 3.3 V analog supply current (Bus A and B active)  | IAVDD3 | fin = 125 MHz, fs = 1 GSPS                               | 1, 2, 3           | 01             |      | 234  | mA   |

| 3.3 V analog supply current (Bus A active)        | IAVDD3 | f <sub>IN</sub> = 125 MHz, f <sub>S</sub> = 1 GSPS       | 1, 2, 3           | 01             |      | 242  | mA   |

| 3.3 V digital supply current (Bus A and B active) | IDVDD3 | fin = 125 MHz, fs = 1 GSPS                               | 1, 2, 3           | 01             |      | 154  | mA   |

| 3.3 V digital supply current (Bus A active)       | IDVDD3 | fin = 125 MHz, fs = 1 GSPS                               | 1, 2, 3           | 01             |      | 85   | mA   |

| Total power dissipation<br>(Bus A and B active)   |        |                                                          | 1, 2, 3           | 01             |      | 2.5  | W    |

| Total power dissipation<br>(Bus A active)         |        |                                                          | 1, 2, 3           | 01             |      | 2.3  | W    |

| Total power dissipation                           |        | ENPWD = logic high (sleep enabled)                       | 1, 2, 3           | 01             |      | 50   | mW   |

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-09240 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>C | SHEET 5    |

TABLE I. <u>Electrical performance characteristics</u> – continued.

| Test                                | Test Symbol |                            | Group A subgroups | Device<br>type | Lin          | nits | Unit |

|-------------------------------------|-------------|----------------------------|-------------------|----------------|--------------|------|------|

|                                     | <u> </u>    | unless otherwise specified |                   | <u> </u>       | Min          | Max  |      |

| Dynamics ac characteristics section | on          | <del>-</del>               | <del>.</del>      | <del></del>    | <del>.</del> |      | 1    |

| Signal to noise ratio               | SNR         | fin = 125 MHz              | 4, 5, 6           | 01             | 54           |      | dBFS |

|                                     |             | fin = 600 MHz              |                   |                | 53.5         |      |      |

|                                     |             | fin = 850 MHz              |                   |                | 53           |      |      |

| Spurious free dynamic range         | SFDR        | fin = 125 MHz              | 4, 5, 6           | 01             | 62           |      | dBc  |

|                                     |             | fin = 600 MHz              |                   |                | 60           |      |      |

|                                     |             | fin = 850 MHz              |                   |                | 56           |      |      |

| Second harmonic                     | HD2         | fin = 125 MHz              | 4, 5, 6           | 01             | 62           |      | dBc  |

|                                     |             | f <sub>IN</sub> = 600 MHz  |                   |                | 60           |      |      |

|                                     |             | f <sub>IN</sub> = 850 MHz  |                   |                | 56           |      |      |

| Third harmonic                      | HD3         | fin = 125 MHz              | 4, 5, 6           | 01             | 62           |      | dBc  |

|                                     |             | fin = 600 MHz              |                   |                | 60           |      |      |

|                                     |             | fin = 850 MHz              |                   |                | 56           |      |      |

| Worst harmonic/spur (other than     |             | f <sub>IN</sub> = 125 MHz  | 4, 5, 6           | 01             | 62           |      | dBc  |

| HD2 and HD3)                        |             | f <sub>IN</sub> = 600 MHz  |                   |                | 60           |      |      |

|                                     |             | f <sub>IN</sub> = 850 MHz  |                   |                | 56           |      |      |

| Total harmonic distortion           | THD         | fin = 125 MHz              | 4, 5, 6           | 01             | 60           |      | dBc  |

|                                     |             | fin = 600 MHz              |                   |                | 58           |      |      |

|                                     |             | fin = 850 MHz              |                   |                | 55           |      |      |

| Signal to noise and distortion      | SINAD       | f <sub>IN</sub> = 125 MHz  | 4, 5, 6           | 01             | 53           |      | dBFS |

|                                     |             | f <sub>IN</sub> = 600 MHz  |                   |                | 52.4         |      |      |

|                                     |             | fin = 850 MHz              |                   |                | 50.8         |      |      |

| Effective number of bits            | ENOB        | fin = 125 MHz              | 4, 5, 6           | 01             | 8.52         |      | Bits |

| (using SINAD in dBFS)               |             | fin = 600 MHz              |                   |                | 8.42         |      |      |

|                                     |             | fin = 850 MHz              |                   |                | 8.16         |      |      |

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-09240 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>C | SHEET 6    |

# TABLE I. <u>Electrical performance characteristics</u> – continued.

| Symbol                      | Conditions $3/$<br>-55°C $\leq$ TC $\leq$ +125°C                | Group A subgroups                                                                                                                                                                                                                                                  | Device<br>type                                                                                                          | Lin   | nits                                   | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | unless otherwise specified                                      |                                                                                                                                                                                                                                                                    |                                                                                                                         | Min   | Max                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                             |                                                                 |                                                                                                                                                                                                                                                                    |                                                                                                                         |       |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (DATA, 0                    | (DATA, OVR/SYNCOUT, CLKOUT)                                     |                                                                                                                                                                                                                                                                    |                                                                                                                         |       |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Vod                         | Terminated 100Ω differential                                    | 1, 2, 3                                                                                                                                                                                                                                                            | 01                                                                                                                      | 247   | 454                                    | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Voc                         | Terminated 100Ω differential                                    | 1, 2, 3                                                                                                                                                                                                                                                            | 01                                                                                                                      | 1.125 | 1.375                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                             |                                                                 |                                                                                                                                                                                                                                                                    |                                                                                                                         |       |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VID                         | Each input pin                                                  | 1, 2, 3                                                                                                                                                                                                                                                            | 01                                                                                                                      | 175   |                                        | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VIC                         | Each input pin                                                  | 1, 2, 3                                                                                                                                                                                                                                                            | 01                                                                                                                      | 0.1   | 2.4                                    | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NB)                         |                                                                 |                                                                                                                                                                                                                                                                    |                                                                                                                         |       |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VIH                         |                                                                 | 1, 2, 3                                                                                                                                                                                                                                                            | 01                                                                                                                      | 2     | AVDD3<br>+ 0.3                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VIL                         | 1, 2, 3 01 0                                                    |                                                                                                                                                                                                                                                                    | 0.8 V                                                                                                                   | V     |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VD, ENA1E                   | BUS)                                                            |                                                                                                                                                                                                                                                                    |                                                                                                                         |       |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VIH                         |                                                                 | 1, 2, 3                                                                                                                                                                                                                                                            | 01                                                                                                                      | 2     | AVDD5<br>+ 0.3                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VIL                         |                                                                 | 1, 2, 3                                                                                                                                                                                                                                                            | 01                                                                                                                      | 0     | 0.8 V                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Digital outputs (SDIO, SDO) |                                                                 |                                                                                                                                                                                                                                                                    |                                                                                                                         |       |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Vон                         | IOH = 250 μA                                                    | 1, 2, 3                                                                                                                                                                                                                                                            | 01                                                                                                                      | 2.8   |                                        | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VoL                         | I <sub>OL</sub> = 250 μA                                        | 1, 2, 3                                                                                                                                                                                                                                                            | 01                                                                                                                      |       | 0.4                                    | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                             |                                                                 |                                                                                                                                                                                                                                                                    |                                                                                                                         |       |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |